Laboratórium 1 - 9. Mérés: Logikai áramkörök vizsgálata

A mérésről

A mérést beugróval kezdtük, 3 kérdés volt:

- TTL alapkapcsolás és működése röviden

- setup time, hold time, propagation time

- mi a latch up, mit lehet ellene tenni

A házi feladatokat gondosan átnézték a mérésvezetők, akiknél gond volt azokat odahívták ki kellett javítani, de segítettek. A mérés során bármikor bármiben ( használható! ) segítséget kaptunk.

Házihoz segítség

Bár a TINA hasznos, meg minden, a mérésvezetők nem nagyon szeretik, eléggé kimeríti a nem megengedett segédeszközt, ne használd a házihoz. Egyszerűen nem tanulsz belőle. Tessék végigbogarászni. Annak idején, amikor ezt a mérést tartottam - jó rég volt - akkor volt ebből gond. Végül addig sikerült gyötörni a hallgatót, amíg rá nem jött, hogyan kell TINA nélkül megoldani.

Alapgondolat: Ne akard kiszámolni. Bemenetre elképzelsz valamilyen kombinációt. Általában diódák vannak utána, ezek szépen nyitnak, ha 1-et kötsz rájuk (mivel nyitóirányú feszültség esik rajtuk). Magyarul logikai 1 van a diódák után is. Tranzisztort hogyan kezeled: ha a bázisán tápfeszültség közeli feszültség van, akkor rövidzár a kollektor és emitter közt. Egyébként szakadás. "Digitálisan" elég jól ki lehet hozni a feladatot.

Feladatmegoldás

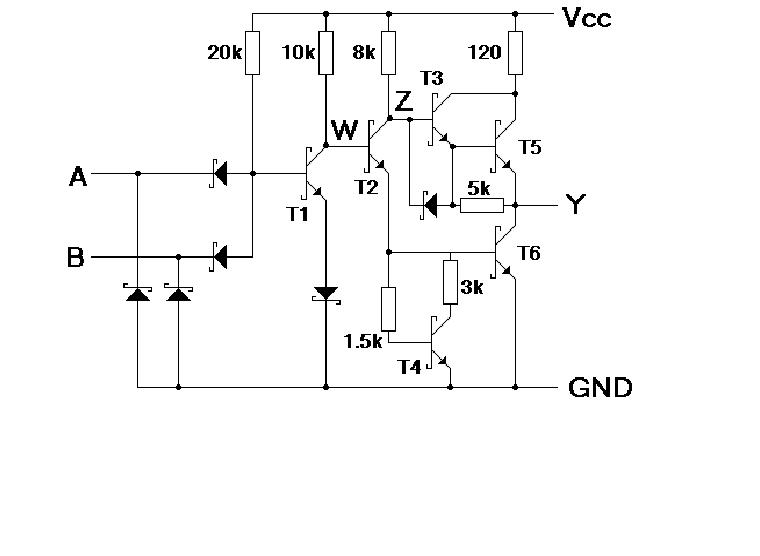

Kapcsolási rajz:

1.1 Kérdés:

Ha A és B földön van (logikai alacsony szint, 0, GND, ahogy "jobban tetszik"),

(/bázisnál/ dióda nyitófesz) - (/emitternél/ dióda nyitófesz) < Tranzisztor nyitófesz

akkor T1 és T2 lezár, olyan mintha szakadás lenne a kollektoruk és emitterük között

--> Z = Vcc - ( T7bázisáram ) * 11k , azaz logikai 1

A Z pont és Y között egy invertert "láthatunk"

(ennek a működését most nincs kedvem részletezni)

Y = Z_negált = GND + U_T6_szat.fesz (vagy T6 maradék fesz), azaz logikai 0 .

Tehát OR kaput valósít meg!

1.2 Kérdés:

Ha A vagy B tápfeszen van (logikai magas szint, 1, VCC, ahogy "jobban tetszik"),

T1 vagy T2 nyitva lesz, amelyik (amelyek) nyitva vannak ~ helyettesíthetők egy rövidzárral, ami a kollektor(uk) és emitter(ük) között húzódik.

Z = (dióda nyitó fesz) , azaz kb. logikai 0 --> T7 zárva lesz, mert bázisa és emittere között nem lesz meg a nyitó feszültség.

T3 nyitva T5 nyitva...

Y = Z_negált = logikai 1

Tehát NOR kaput valósít meg!

1.3 Kérdés:

Határozza meg, hogy hogyan változik a tranzisztorok állapota, ha az A lábon 0-tól 5 V-ig folyamatosan emeljük a feszültséget és a másik lábra 0 V-ot adunk!

TINA szimuláció eredménye:

1.4 Kérdés:

Határozza meg, hogy hogyan változik a tranzisztorok állapota, ha az A lábon 0-tól 5 V-ig folyamatosan emeljük a feszültséget és a másik lábra 5 V-ot adunk!

Feladatmegoldás 2

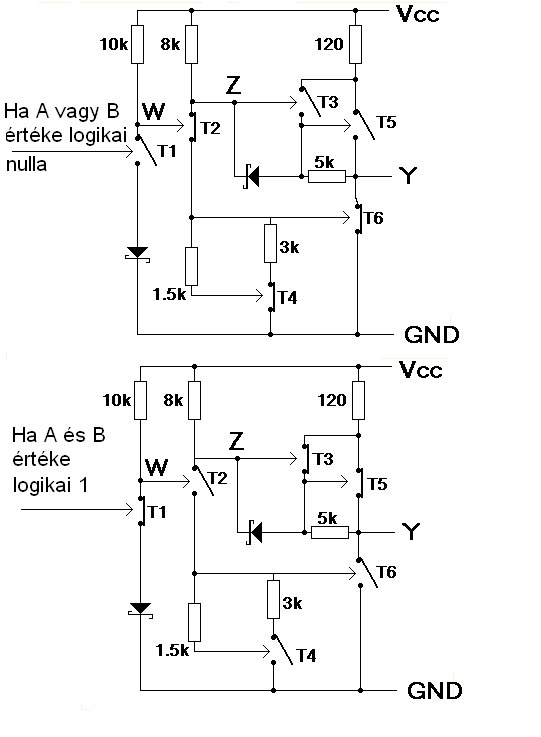

Kapcsolási rajz:

Működést szemléltető ábra:

Komment a rajzhoz: A rajzban vezérelt kapcsolókkal helyettesítem a tranzisztorokat. Logikai 0 vezérlő jel esetén a kapcsoló tulajdonképpen szakadás, logikai 1 vezérlés esetén a kapcsoló átvezet. A lent olvasható leírásban: Ha egy tranzisztor NYITVA van, az a kapcsoló ZÁRT állapotának felel meg, ha a tranzisztor ZÁRVA van, az kapcsoló NYITOTT állapotának (szakadásnak) Gondolj bele! Az 1. esetnek a képen az alsó, a 2. esetnek a felső ábra felel meg.

Huzalozott ÉS (AND)-nek (is) tekinthető a bemeneti rész (T1 bázisa..).

Olvasás közben nézd az ábrát.. (közelítő számítások: a Diódát "idelálisnak" veszem, azaz csak a nyitófeszültségét veszem figyelembe (~0,7V), a Tranzisztornak a bázisáramával sem számolok.., nyitófeszültségét ~0,7V-nak veszem)

"Két" eset lehetséges logikai szempontból T1 vagy nyitva van vagy zárva.

1. eset:

T1 nyitva ha bázisa és emittere között nyitófeszültségnyi esik (BJT esetén (szoba hőmérsékleten) <~0,7V), ez akkor van ha a bázisa a földhöz (GND) képest 2* nyitófeszültségnyire van (~1,4V) (mivel T1 emittere és a föld között ott van egy Schottky dióda.. (annak is van nyitó feszültsége.. ~0,7V)). A bemeneteknek (A és B) ilyenkor a T1 bázisán lévő potenciálhoz képest nem lehetnek (a Schottky diódák) nyitófesz.-nyivel alacsonyabb potenciálon (földhöz (GND) képest (a két pont külön-külön) nem lehet ~0,7V -alatt) Logikai szempontból A és B is logikai 1 szintű.. Ha T1 nyitva van akkor kollektora és emittere közötti feszültség közel 0V (maradék fesz. esik rajta ~0,1V), ekkor T2 zárva van mivel bázisa és emittere között nem esik nyitófesz nagyságú feszültség.(T2 bázisa a földhöz (GND) képest ~0.7V-nyira van (Dióda nyitó fesz+T1 maradék fesz.) //T2 nyitásához a bázisának a földhöz képest (GND) ~1.4 V-nyira kell lennie mivel ha T2 nyitva van akkor T6 is nyitva lesz, ebben az esetben viszont T6 bázisa ami T2 emittere a földhöz (GND) képest nyitófesz.-nyire van..//) T6, T4 zárva (mivel T2 zárva). T3-T5 nyitva ("képzelj" egy ellenállást az Y és GND közé) (együttes nyitófeszültségük ~1.4V). Tehát logikai szinteket nézve W=0, Y=1, Z=1.

2. eset:

T1 zárva ha a bázisa és a föld (GND) közötti feszültség esés kisebb mint 2*nyitófesz ( <~1.4V). Ez akkor áll fenn ha a bemenetek (A vagy B) közül legalább az egyik földhöz (GND) képesti potenciálja kisebb mint nyitófesz. (<~0.7V), mert akkor T1 lezár. T2 nyitva van mivel bázisa 2*nyitófesz.-nyire (~1.4V) van a földhöz (GND) képest. T6 is nyitva van. Ezekből T3 bázisa (alias Z) ~0.8V-nyira van (T6 nyitófesz.+ T2 maradék fesz), ezért T3-T5 zárva. Tehát logikai szinteket nézve W=1, Y=0, Z=0.

T4 nyitva lehet ha T2 nyitva van..

Igazságtábla:

| A | B | W | Y | Z |

|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 |

W kimeneten NAND

Y kimeneten AND

Z kimeneten AND

Beugró kérdések kidolgozása

Ezt a részt még aktualizálni kell. Nem biztos, hogy még mindig ezek a beugrókérdések!

Egy drága jó FF-os kérdés

A példa: D-FF CLK bemenetén inverteren át jön az órajel, és a D bemene elé is teszünk egy invertert, így kapunk egy negatív élvezérelt D-FF-ot. Adottak t_setup_max és t_hold_max, továbbá az inverterek fel-/lefutási idejei, azaz "késleltetései":

Felfutási idő minimum t_HL_min, maximum t_HL_max lehet, lefutási időre ezek: t_LH_min, t_LH_max. Ezeket én úgy értelmeztem, hogy ha az inverter bemenetén például HL van, akkor a kimenetére a LH ennyi idővel érkezik meg maximum ill. minimum.

Ezek után rajzolunk egy idődiagramot, majd a legrosszabb esetre gondolunk bele a helyzetbe.

t_setup akkor maximális, ha a D bemenet kezdeti váltása a lehető legjobban balra van csúszva, és a CLK bemenet a lehető legjobban jobbra van elcsúszva. Előbbi nem teljesül, mert olyan állat nincs, ami balratol valamit egy idődiagramon, max egy időgép. D viszont mindenképp eltolódik jobbra min(t_LH_min, t_HL min) [a kettő közül a kisebb] értékkel. A CLK bemeneten mintavételező pozitív él (ami az előtte levő inverteren negatív, HL él) maximális késése t_HL_max. Így t_setup_max_új = t_setup_max + t_HL_max - min(t_LH_min, t_HL_min)

t_hold akkor maximális, ha a lehető legelőrébb van az órajel felfutó éle (azaz az a megkésett ám, de invertált HL) , és leghátrébb van D-nek vége. Így t_hold_max_új = t_hold_max + max(t_LH_max, t_HL_max) - t_HL_min

TTL és CMOS inverterek fogyasztása

A tápfesz mindegyiknél 5V, ezt szoroztam a tápárammal, amit vagy Quiescent (nyugalmi) áramként vagy ICC-ként emlegetnek az adatlapok. Ha alacsony szint a kimenet, akkor tud a legnagyobbat fogyasztani, ha magas a kimenet, akkor pedig a legkevesebbet, így jöttek ki a +- értékek.

| Típus | I_CC [mA] | P [mW] |

| MM74HC04 | ||

| MM74HCT04 | ||

| 74AC04 | ||

| 74ACT04 | ||

| 74F04 | ||

| DM74ALS04B | ||

| DM74AS04 | ||

| sn7404 | ||

| sn74ls04 |