| 1. Mark the true statements with an X and the false statements with a – in the last column. Each good and 0.5 points, each wrong answer -0.5 points, and an empty answer 0 point. Total of 0 to 3 points. | swer is       |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|

| The Neumann architecture computer stores the instructions and data in the same memory, and in the same format.                                                                                            |               |  |  |  |

| The CPU can use a microprogrammed control unit for faster instruction execution.                                                                                                                          |               |  |  |  |

| In a multitasking system, each task is assigned to an individual physical processor.                                                                                                                      |               |  |  |  |

| The Cache is used to make the memory apparently faster to the user.                                                                                                                                       |               |  |  |  |

| The Cache makes data transfer between the virtual and physical memory faster.                                                                                                                             |               |  |  |  |

| A Harward architecture computer can be faster because it can read from two memories at the same time.                                                                                                     |               |  |  |  |

| 2. Mark the true statements with an X and the false statements with a – in the last column. Each good and 0.5 points, each wrong answer -0.5 points, and an empty answer 0 point. Total of 0 to 3 points. | swer is       |  |  |  |

| A zero address machine always needs to have a stack.                                                                                                                                                      | (3p)          |  |  |  |

| A four address machine has to have a program counter.                                                                                                                                                     |               |  |  |  |

| Tasks on an x86 based system can call themselves (can be recursive).                                                                                                                                      |               |  |  |  |

| During a task switch, the internal state of the processor is saved entirely by sofware.                                                                                                                   |               |  |  |  |

| The Task State Segment (TSS) is a descriptor data structure that stores the actual state of a task's execution.                                                                                           |               |  |  |  |

| In case of the x86, the number of bits used to indicate the starting address of a page does not depend on the actually implemented size of the physical memory.                                           |               |  |  |  |

| 2. What is the manage of a TACK CATE in the v96 analyte stance?                                                                                                                                           |               |  |  |  |

| 3. What is the purpose of a TASK GATE in the x86 architecture?                                                                                                                                            |               |  |  |  |

|                                                                                                                                                                                                           | (2 <i>p</i> ) |  |  |  |

|                                                                                                                                                                                                           |               |  |  |  |

|                                                                                                                                                                                                           |               |  |  |  |

|                                                                                                                                                                                                           |               |  |  |  |

| 4. Which descriptor tables can contain CALL GATEs in the x86 architecture?                                                                                                                                |               |  |  |  |

|                                                                                                                                                                                                           | (1)           |  |  |  |

|                                                                                                                                                                                                           | (1 <i>p</i> ) |  |  |  |

|                                                                                                                                                                                                           |               |  |  |  |

|                                                                                                                                                                                                           |               |  |  |  |

|                                                                                                                                                                                                           |               |  |  |  |

| 5. A cache uses a <b>4 way set associative mapping</b> scheme. The block size is 256 bytes, the whole cache stores 1024 blocks. There <b>is one extra bit</b> in the control stores to indicate validity of each block. The physical address is 32 bits long. |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| a) <b>How long is the offset</b> part of the address?                                                                                                                                                                                                         |  |

| a) <b>How long is the offset</b> part of the address?                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                                                                               |  |

|                                                                                                                                                                                                                                                               |  |

| b) What is the organization of a Control Store (words x bits)? (2 points)                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                                                               |  |

| c) How many TAG comparators are there in the cache?                                                                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                               |  |

| 6. Draw the signal pattern of the writing current in case of PE, FM and MFM modulation |     |   |   |   |   |   |  |  |

|----------------------------------------------------------------------------------------|-----|---|---|---|---|---|--|--|

|                                                                                        | 00  | 1 | 1 | 0 | 0 | 1 |  |  |

|                                                                                        | PE  |   |   |   |   |   |  |  |

|                                                                                        | FM  |   |   |   |   |   |  |  |

|                                                                                        | MFM |   |   |   |   |   |  |  |

(*3p*)

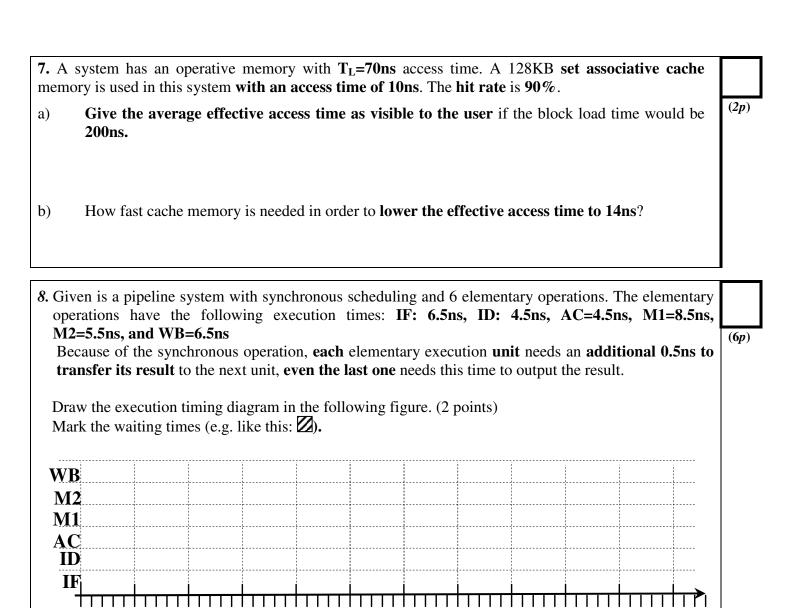

How long is the latency? (1 point)

Give the value of the restart time. (1 point)

Give the efficiency of the pipeline. (2 point)

| 9. A computer system uses an <b>index register</b> memory extension system. <b>The logical address space is 64KBytes, the physical address space</b> (memory size) <b>is 256KBytes</b> . The first 4 bits of the logical address are used as index. Additional 2 bits are used for control (they are before the address extension |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| bits). Draw the layout of the index register array (1 point).                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Give the size (number of registers, number of bits) of the index register array. (2 points)                                                                                                                                                                                                                                       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| In this system, we want to run a <b>program</b> that is compiled <b>to start at address (63FFh)</b> and has a <b>size</b> of <b>8KBytes</b> . Which <b>register(s)</b> do we need <b>to set</b> in the index register array? (1 point)                                                                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| In the physical memory, there is free space between 17000h and 17FFFh (4KB space) and after 30000h up to the end of physical memory (3FFFFh).                                                                                                                                                                                     |  |  |  |  |

| What value(s) should we set to the given index registers? (there are many possible good answers) (1 point)                                                                                                                                                                                                                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |