# Budapest University of Technology and Economics Department of Electron Devices

## **Technology of IT Devices**

#### Lecture 1

- Lecturers and Administration

- Course Requirements

- Lab Timing and Softwares

- Course Topics/Syllabus

- Basic Concepts of Semiconductors

- Microelectronics & Integrated Circuits IC's

- Trends in Integrated Circuit Technology

#### Lecturers and Administration

- Ahmed I M Alnahhal

— PhD student

- <u>aalnahhal@edu.bme.hu</u>

- Office: Q.B313

- AL-abassi Salam Abd Al-Ameer Waheed PhD student

- sal-abassi@edu.bme.hu

- Office: Q.B313

The course can be found on EDU: Edu.vik.bme.hu

## PLEASE DO NOT RECORD THE LECTURES!

## **Course Requirements**

- Five computer laboratories

- They will be marked as pass or fail.

- One lab can be retaken.

- One midterm test at the end of this semester (in-person)

- It also can be retaken.

- You must pass both the labs and the midterm test to pass this course.

- Final grade will be calculated, based on the result of the midterm test:

- 0-40% : fail (1)

- 41-55%: satisfactory (2)

- 56-70%: average (3)

- 71-85%: good (4)

- 86-100%: excellent (5)

## Lab Timing and Softwares

- There will be Five labs on odd weeks (please check the time table).

- The first lab will be on September 24th (Friday).

- The lab materials will be uploaded to EDU too.

- LTspice

- For basic analog and digital circuits

- FloTerm

- For basic analog and digital circuits

## Course Topics/Syllabus

- 1. Microelectronics and IC Introduction

- 2. Microelectronics (CMOS)

- 3. IC Manufacturing Technology

- 4. IC Packaging\_1

- 5. IC Packaging \_2

- 6. Parasitic effects of packaging

- 7. Thermal effects on IC packaging\_1

- 8. Thermal effects on IC packaging\_2

- 9. Design flow of electrical equipment

- 10.Introduction to signal integrity\_1

- 11.Introduction to signal integrity\_2

## **Basic Concepts of Semiconductors**

- What does semiconductor mean?

- What material are transistors made of?

- How does it work?

- Why is it suitable to create a logic gate?

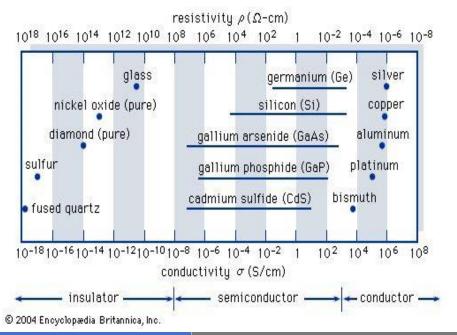

Semiconductors' conductance is between that of conductors and

insulators

#### They conduct current

- Semiconductors have a negative thermal coefficient (NTC)

- It means their conductivity increases when temperature rises.

- This is exactly the opposite behaviour of metals.

#### ■ The most important semiconductors:

- Monocrystalline or single-crystal materials:

- Semiconductor elements: Si (silicon), Ge (germanium)

- Compound semiconductors: GaAs (gallium arsenide), GaAsP (gallium arsenide phosphide). They are

used to create LEDs.

- Amorphous semiconductors: amorphous Si mainly

- Organic semiconductors: OLEDs (Organic LEDs)

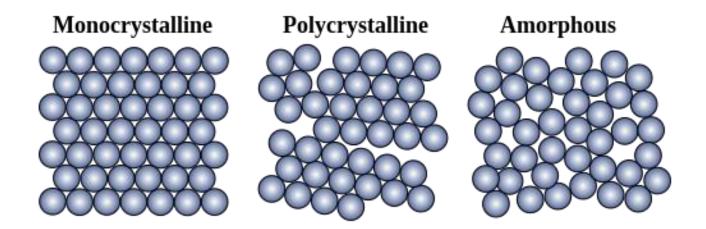

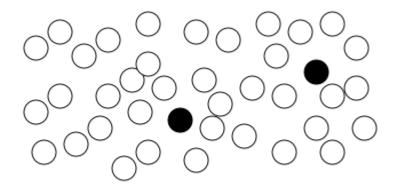

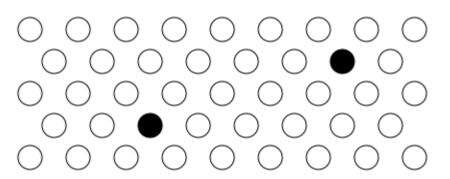

### **Types of Crystal**

- Crystalline: materials in which atoms are placed in a high ordered structure.

- Poly-crystalline: These materials consist of small crystalline regions with random orientation called grains, separated by grain boundaries.

- Amorphous: materials in which atoms are placed randomly.

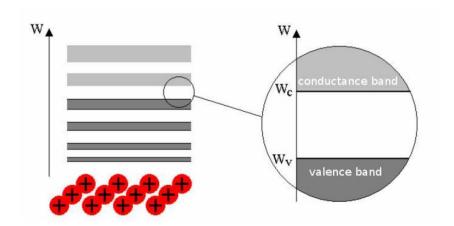

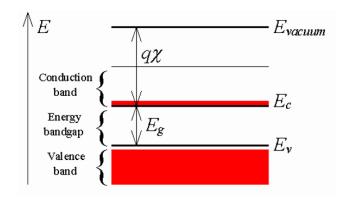

#### The Energy band structure

- An electron's energy is a quantized quantity. When electrons take part in a system, every electron has to be at a different energy level.

- Complete energy band diagrams are very complex. The energy levels are grouped in bands, separated by energy band gaps.

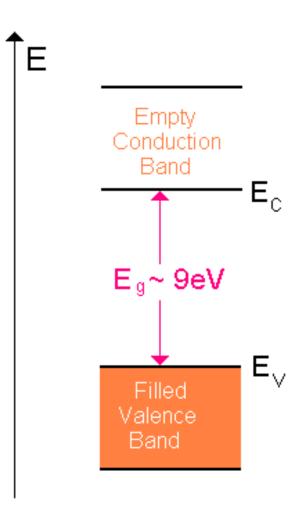

## **Energy band of Insulator:**

- Large bandgap.

- All the energy levels in the valence band are occupied by electrons

- All energy levels in the conduction band are empty.

- Thermal energy or an applied electric field cannot raise the uppermost electron in the valence band to the conduction band.

- It cannot conduct current

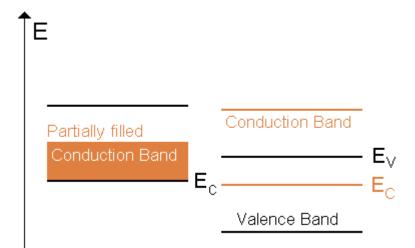

# **Energy band of Conductors:**

- The conduction band overlaps the valence band so that there is no bandgap.

- The conduction band is partially filled.

- The uppermost electrons in the partially filled band or electrons at the top of valence band can move to the nexthigher available energy level when they gain kinetic energy.

- They conduct current

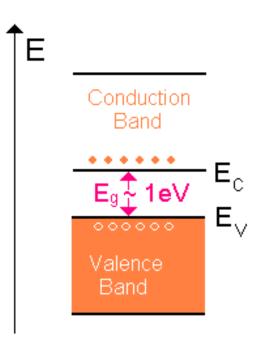

# **Energy band of Semiconductors:**

- Bonds between neighboring atoms are only moderately strong

- Some electrons will be able to move from valence band to the conduction band, leaving holes in the valence band.

- When an electric field is applied, electrons and holes will gain kinetic energy and conduct electricity

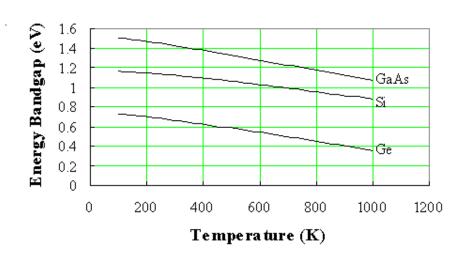

## Temperature dependence of the energy bandgap:

- The energy bandgap of semiconductors tends to decrease as the temperature is increased.

- The variation of bandgaps with temperature can be expressed:

$$E_g(T) = E_g(0) - \frac{\alpha T^2}{T + \beta}$$

|                         | Silicon | GaAs  | Germanium |

|-------------------------|---------|-------|-----------|

| E <sub>g</sub> (0) (eV) | 1.166   | 1.519 | 0.7437    |

| α (meV/K)               | 0.473   | 0.541 | 0.477     |

| β (K)                   | 636     | 204   | 235       |

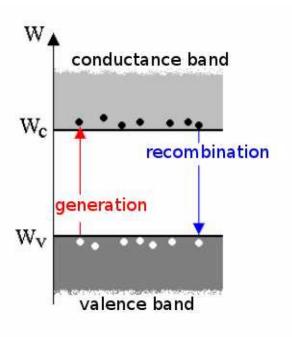

#### **Charge carriers**

■ Electrons: at the bottom of the conductance band while the holes at the top of the valence band — a hole is an absence of electron.

- Generation: happens when an electron gets to the conductance band from the valence band.

- This means that two charge carriers are created: an electron in the conductance band and a hole in the valence band.

Recombination: the opposite of generation – when an electron falls back to the valence band.

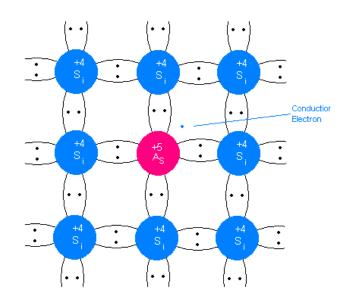

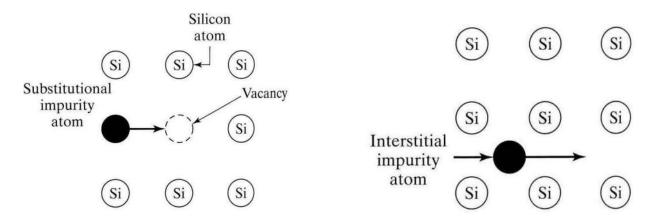

### **Doping**

■ A small number of atoms of a different element are injected into the crystal structure. Therefore, dopants are placed in positions where Si atoms are normally located.

- There are two types of doping

- 1. n-type doping

- The generation of free carriers requires not only the presence of impurities, but also that the impurities give off electrons to the conduction band in which case they are called donors.

- Electrons are the majority charge carriers, holes are the minority charge carriers

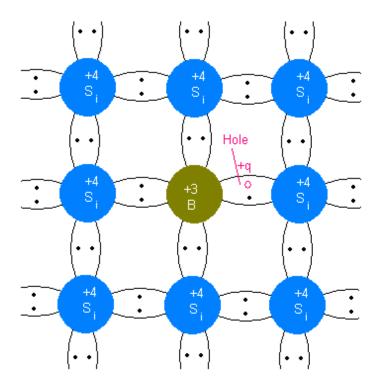

#### 2. p-type doping:

- The impurities give off holes to the valence band, in which case they are called acceptors

- Electrons are the minority charge carriers, holes are the majority charge carriers

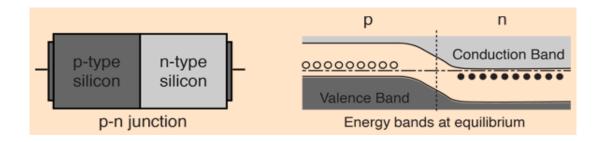

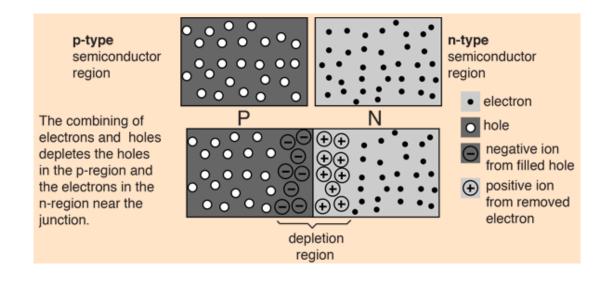

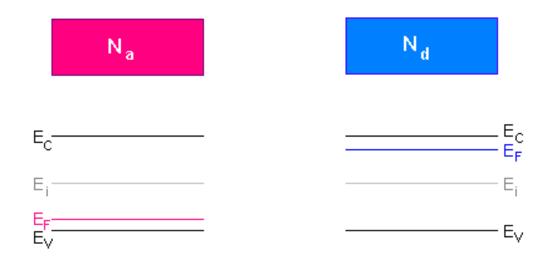

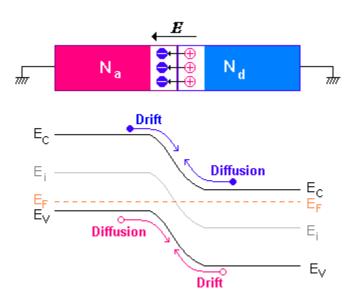

## The pn-junction (a semiconductor diode)

#### Circuit Environment

- A p-n junction consists of two semiconductor regions with opposite doping type.

- The p-type semiconductor has an acceptor density N<sub>a</sub>.

- The n-type has a donor density N<sub>d</sub>.

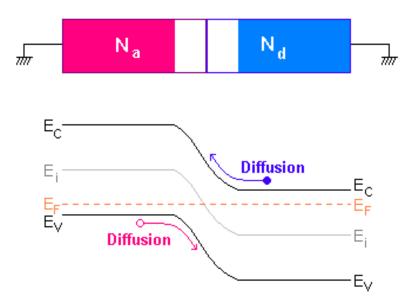

- The large carrier concentration gradients at the junction cause carrier diffusion:

- Holes from the p-side diffuse into the n-side

- Electrons from the n-side diffuse into the p-side

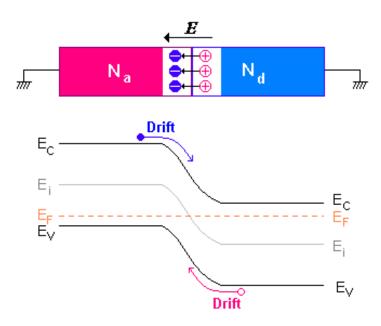

- Negative space charge near the p-side of the junction: As holes continue to leave the p-side, some of the negative acceptor ions (N<sub>a</sub>-) near the junction are left uncompensated.

- A **positive space charge** near the n-side: some of the positive donor ions (N<sub>d</sub>+) near the junction are left uncompensated as the electrons leave the n-side.

- At thermal equilibrium (steady-state condition) without external excitations, the net current flow across the junction is zero.

- The Fermi level must be constant (condition of zero net electron and hole current)

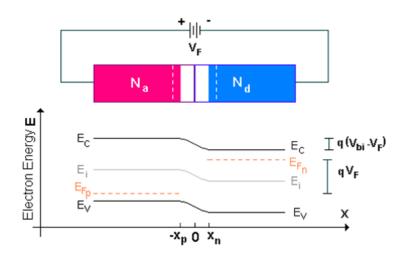

- Forward-biased p-n junction:

- positive voltage "V<sub>F</sub>" applied to the p-side.

- The depletion width decrease with the increasing of the applied voltage:

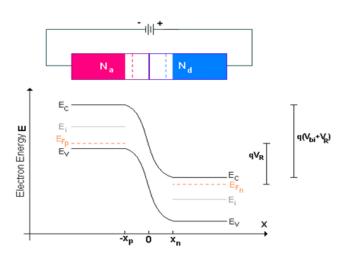

- Reverse-biased p-n junction:

- positive voltage "V<sub>R</sub>" applied to the n-side.

- The depletion width increases with the increasing of the applied voltage:

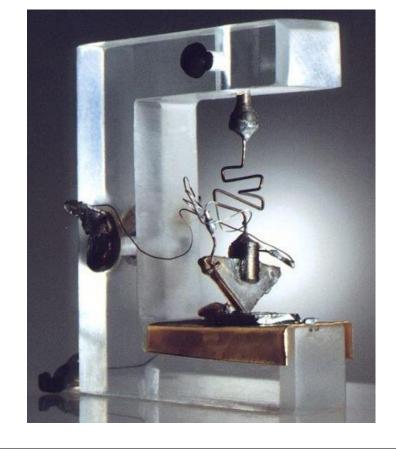

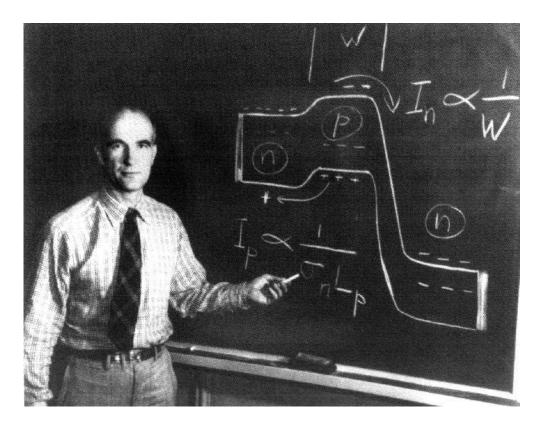

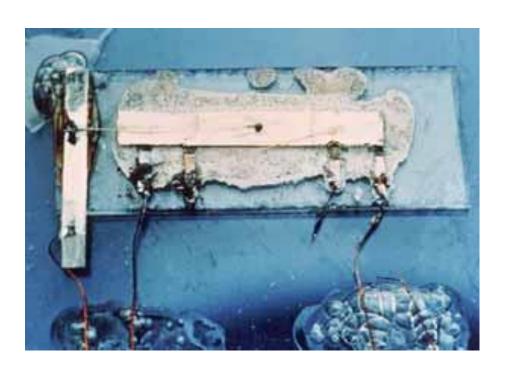

#### The Transistor Era

• 1947 - John Bardeen, Walter Brattain, and William Shockley invented the first Transistor: the Point-Contact

Transistor, at Bell Laboratories.

• 1948 - **Shockley** invents junction transistor:

Three layers of semiconductors all piled together. The junction Transistor involved current flowing directly through the chunks of semiconductors, not along the surface.

#### Circuit Environment

- 1954 First Transistor Radio

- 1954 First fully transistorized computer

- 1956 Nobel Prize Awarded to Shockley, Brattain & Bardeen

- 1958 J. Kilby invents integrated circuit at the Texas Instruments Lab

#### **History**

- 1906 Semiconductors used to detect radio signals

- 1925 FET concept patent by J. Lilienfeld1941 Z3 by Konrad Zuse

first computer

- 1946 ENIAC first electronic computer

- 1947 Transistor "Invented"

- ☐ AT&T ignores LilienfeldBardeen,

- ☐ Brattain and Schockley, AT&T, Nobel Prize in 1956

- 1958 Integrated Circuit

- ☐ Kilby & Noyce (died 1990)

- ☐ Kilby Noble Prize in 2000

- 1960- MOSFET manufactured and patented

- 1963- CMOS logic invented

- ☐ Resistors replaced by transistorsMicro transductors '08, CMOS Basics

Circuit Environment

https://youtu.be/7ukDKVHnac4

## Microelectronics& Integrated Circuits IC's

- Microelectronics is a subfield of electronics, and it relates to the study and manufacturing of very small electronic designs and components

- These devices are typically made from semiconductor materials.

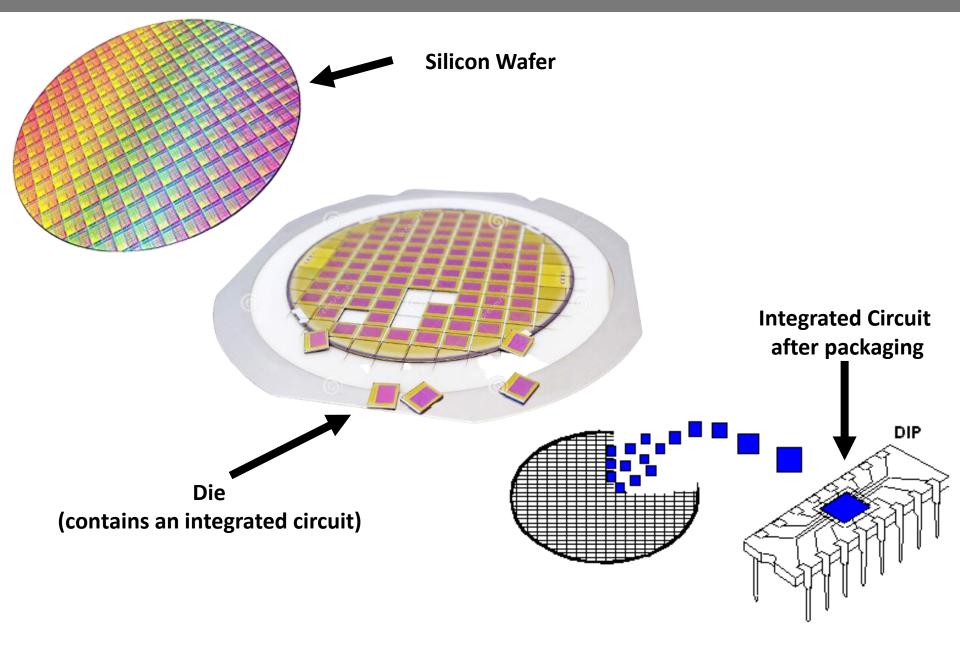

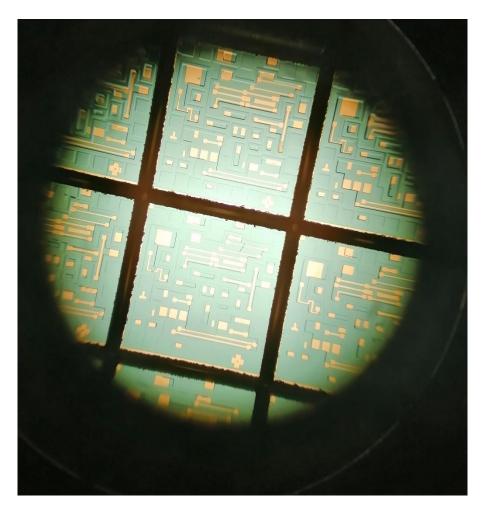

- An integrated circuit (IC), sometimes called a chip or microchip, is a semiconductor wafer on which thousands or millions of tiny resistors, capacitors, and transistors are fabricated.

- An IC can function as an amplifier, oscillator, timer, counter, computer memory, or microprocessor.

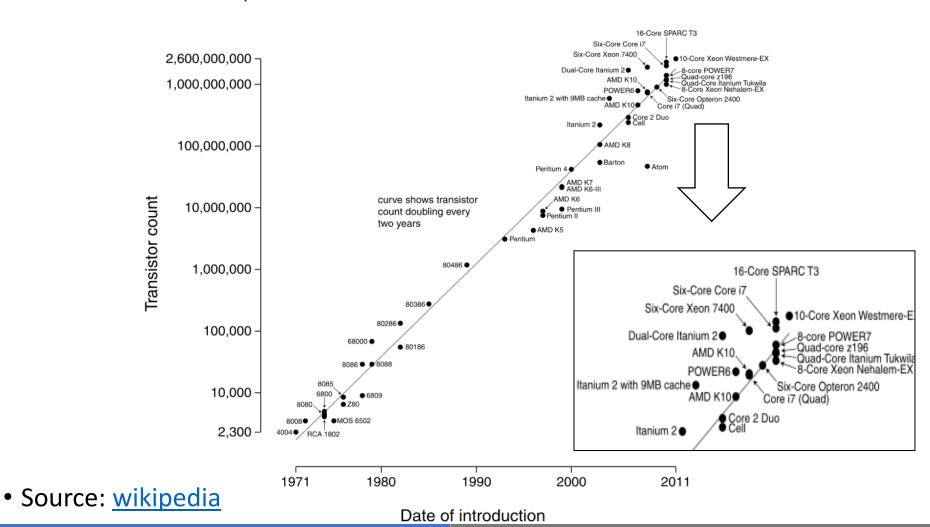

#### Moore's law

- Gordon Moore made a prediction in 1965, that the number of transistors integrated on one chip would double every 18-24 month (exponential growth).

- The 1 million transistors per chip barrier was broken through in the 80's:

- 1971: 2300 transistors, clock frequency: 1 MHz (Intel 4004)

- 2001: 42 million transistors, clock frequency: 2 GHz (Intel P4) 2001

- 2016: 7.2 billion transistors, 22-core Xeon Broadwell-E5

- 2.2GHz (3.6GHz in turbo mode), 55MB smart cache, 456mm<sup>2</sup>

- FPGA: 30 billion transistors, Stratix 10 10GX5500/10SX5500

#### **Evolution of Microprocessors**

#### Microprocessor Transistor Counts 1971-2011 & Moore's Law

- Integrated circuits can be classified into two groups based on the type of transistors they contain.

- 1. Bipolar integrated circuits contain bipolar junction transistors as their principle elements.

- 2. Metal-oxide-semiconductor (MOS) integrated circuits contain MOS transistors as their principle elements.

- Integrated circuits are also categorized according to the number of transistors or other active circuit devices they contain.

- 1. A small-scale integration (SSI) IC contains fewer than 10 transistors.

- 2. A medium-scale integration (MSI) IC contains from 10 to 100 transistors.

- 3. A large-scale integration (LSI) IC contains from 100 to 1,000 transistors.

- 4. A very-large-scale integration (VLSI) contains more than 1,000 transistors.

- All ICs now employ VLSI, and these distinctions are only of historical importance.

- Some integrated circuits are analog devices; an operational amplifier is an example.

- Other ICs, such as the microprocessors used in computers, are digital devices.

- Some hybrid integrated circuits contain both analog and digital circuitry; a bilateral switch, which switches analog signals by means of a digital control signal is an example of a hybrid IC.

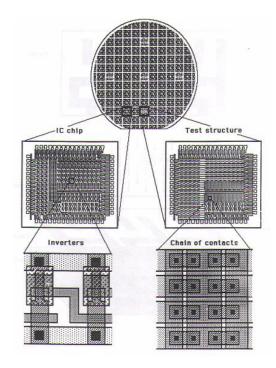

#### **Planar technology**

- Very large scale integration (VLSI) is the process of creating an integrated circuit (IC) by combining millions of MOS transistors onto a single chip.

- Most ICs had a limited set of functions they could perform. An electronic circuit might consist of a CPU, ROM, RAM and other glue logic. VLSI enables IC designers to add all of these into one chip.

- The word planar implies that the devices are fabricated on the surface of the silicon wafer in a 2D structure.

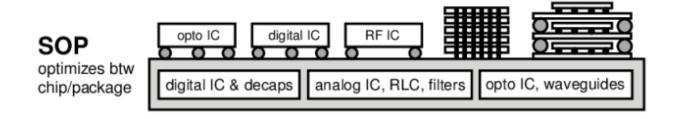

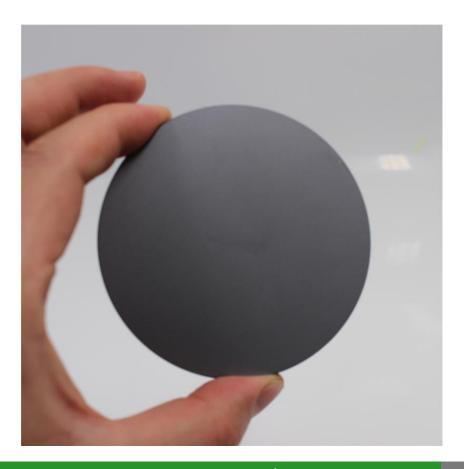

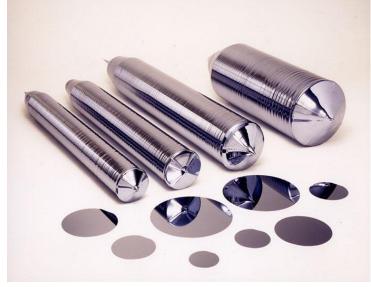

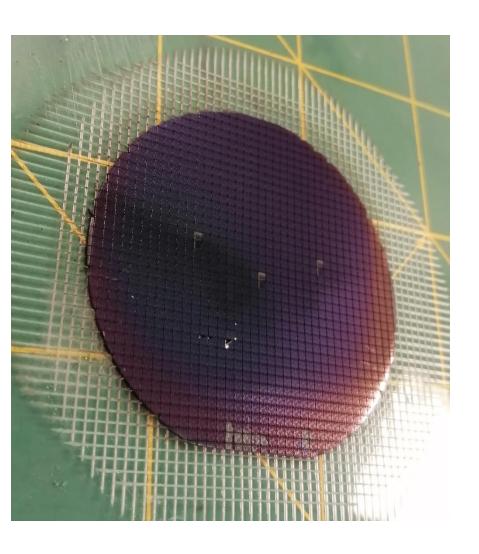

- The basis is a silicon ingot made up of monocrystalline silicon.

The ingot is sliced into wafers. A wafer can contain thousands of ICs that are manufactured at the same time.

## Trends in Integrated Circuit Technology

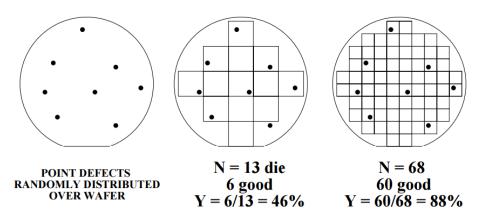

- The number of components can be increased in two ways

- Increasing the size of the chip.

- But it ends up with more failures per wafer (lower yield) due to randomly distributed defects on wafers.

- Optimal chip area is about 500mm<sup>2</sup>

- If we can decrease every physical size by the factor of 2, we can produce 4 times more components. This is called scaling

- Effects of scaling

- Delay can be decreased (clock frequency can be increased)

- Power consumption of logic gates decreases

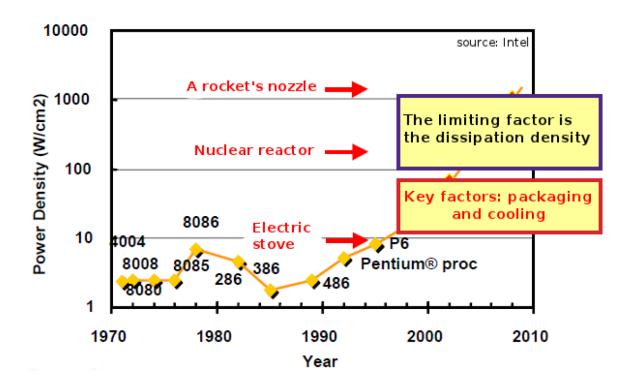

- Power dissipation density increases!

## Dissipation density

If scaling continues at present pace, high speed processors would have power density of nuclear reactor by 2005, a rocket nozzle by 2010 and a surface of the sun by 2015!

#### Why Power Matters

- 1. Packaging costs.

- 2. Power supply rail design.

- 3. Chip and system cooling costs.

- 4. Noise immunity and system reliability.

- 5. Battery Life (in portable systems).

- This reason led us to design multi-core processors

- 2004: Power Wall, which has limited the frequency to 3-4GHz

IC)

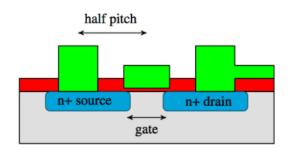

- A specific semiconductor process has specific rules on the minimum size and spacing for features on each layer of the chip.

- The half pitch of the first metallization layer is the defining feature for chips. The gate width represents the smallest feature.

- The shrinking trend of feature size led to the classification of different generations of ICs, giving rise to new design methods from the early small-scale integration (SSI) to the more complex ultra-large-scale integration (ULSI)

and three-dimensional integrated circuit (3D-

## **Technology node**

- The technology node (also process node, process technology) refers to a specific semiconductor manufacturing process and its design rules.

- Historically, the process node name referred to a number of different features of a transistor including the gate length as well as half-pitch.

- Generally, the smaller the technology node means the smaller the feature size, producing smaller transistors which are both faster and more power-efficient.

# MOSFET scaling (process nodes)

```

10 \mu m - 1971

6 \mu m - 1974

3 \mu m - 1977

1.5 \mu m - 1981

1 \mu m - 1984

800 nm - 1987

600 nm - 1990

350 nm - 1993

250 nm - 1996

180 nm - 1999

130 nm - 2001

90 nm - 2003

65 nm - 2005

45 nm - 2007

32 nm - 2009

22 nm - 2012

14 nm - 2014

10 nm - 2016

7 nm - 2018

5 nm - 2020

```

Future<u>3 nm</u> ~ 2022 2 nm ~ 2024

- The ITRS roadmaps always contain the latest predictions and directions of the development.

- They are created by the leaders of the industry.

- Forecast from 2015 can be found here.

| YEAR OF PRODUCTION                           | 2015    | 2017    | 2019   | 2021                   | 2024         | 2027         | 2030         |

|----------------------------------------------|---------|---------|--------|------------------------|--------------|--------------|--------------|

| Logic device technology naming               | P70M56  | P48M36  | P42M24 | P32M20                 | P24M12G1     | P24M12G2     | P24M12G3     |

| Logic industry "Node Range"<br>Labeling (nm) | "16/14" | "11/10" | "8/7"  | "6/5"                  | "4/3"        | "3/2.5"      | "2/1.5"      |

| Logic device structure options               | FinFET  | FinFET  | FinFET | FinFET<br>LGAA<br>VGAA | VGAA,<br>M3D | VGAA,<br>M3D | VGAA,<br>M3D |

We will revisit these abbreviations (FinFET, FDSOI, LGAA, VGAA) later

# Budapest University of Technology and Economic Department of Electron Devices

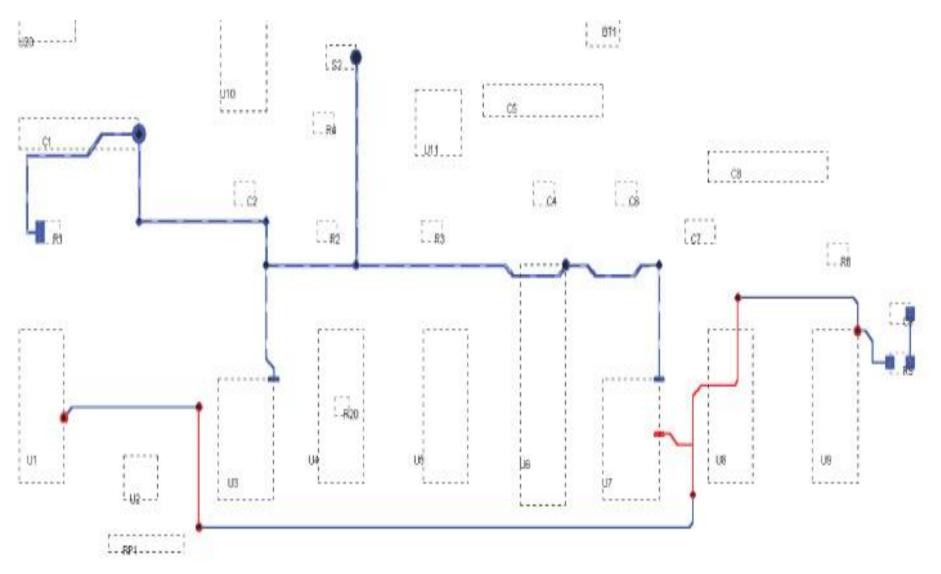

# **Circuit Environment**

## Lecture 2

- Field Effect Transistors Classification

- MOSFET Transistors

- The Operation of MOSFET Transistor

- Fabrication Process Technologies

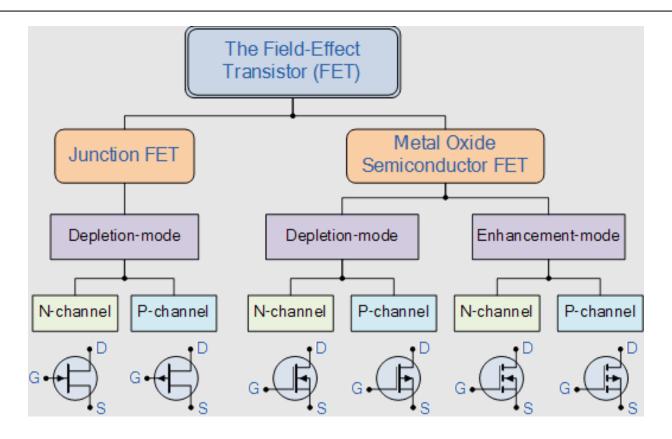

#### **Field Effect Transistors classification**

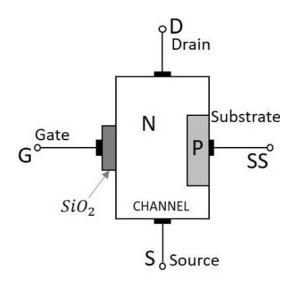

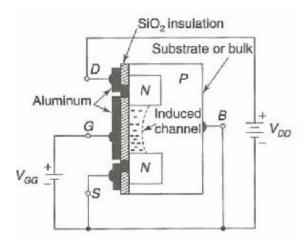

MOSFET differs from a JFET in that it has a "Metal Oxide" Gate electrode

which is electrically insulated from the main semiconductor n-channel or pchannel by a very thin layer of insulating material usually silicon dioxide.

#### **MOSFET Transistors**

- MOS: Metal-Oxide-Semiconductor

- MOSFETs are three terminal devices with a Gate, Drain and Source and both P-channel (PMOS) and N-channel (NMOS) MOSFETs are available.

- The Substrate terminal is not normally used as either an input or an output connection but instead it is used for grounding the substrate.

- The MOSFET acts like a voltage controlled resistor as the current flowing through the main channel between the Drain and Source is proportional to the input voltage.

- The MOSFETs are available in two basic forms:

- Depletion Type the transistor requires the Gate-Source voltage, ( $V_{GS}$ ) to switch the device "OFF". The depletion mode MOSFET is equivalent to a "Normally Closed" switch.

- Enhancement Type the transistor requires a Gate-Source voltage, ( $V_{GS}$ ) to switch the device "ON". The enhancement mode MOSFET is equivalent to a "Normally Open" switch.

- Both the Depletion and Enhancement type MOSFETs use an electrical field produced by a gate voltage to alter the flow of charge carriers, electrons for n-channel or holes for P-channel, through the semiconductive drain-source channel.

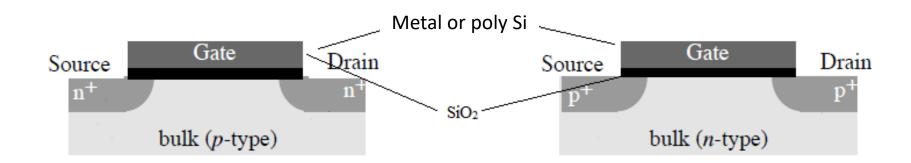

- There are two types of MOS transistors.

- nMOS: the bulk is p-type silicon (the inversion channel is n-type)

- pMOS: the bulk is n-type silicon (the inversion channel is p-type)

# The Operation of MOSFET Transistor

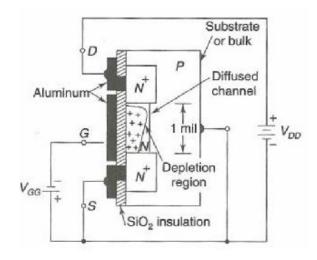

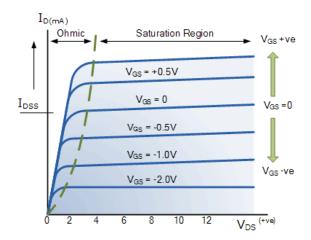

- Depletion-mode MOSFET

- The drain-source channel is conductive with the electrons and holes already present within the n-type or p-type channel. This doping of the channel produces a conducting path of low resistance between the drain and source with zero Gate bias.

- It normally switched "ON" (conducting) without the application of a gate bias voltage. That is the channel conducts when  $V_{GS} = 0$ , making it a "normally-closed" device.

- For the n-channel depletion MOS transistor, a negative gate-source voltage,  $V_{GS}$  will deplete the conductive channel of its free electrons switching the transistor "OFF".

Likewise for a p-channel depletion MOS transistor a positive gate-source voltage, + V<sub>GS</sub>

will deplete the channel of its free holes turning it "OFF".

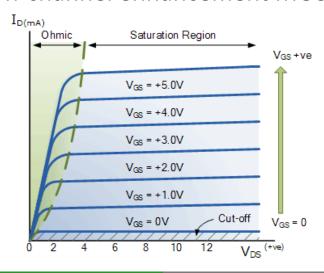

The I-V Characteristic of n-channel depletion MOS transistor is:

#### Enhancement-mode MOSFET

- Here the conducting channel is lightly doped or even undoped making it non-conductive. This results in the device being normally "OFF" (non-conducting) when the gate bias voltage,  $V_{GS}$  is equal to zero.

- For the n-channel enhancement MOS transistor a drain current will only flow when a gate voltage ( $V_{GS}$ ) is applied to the gate terminal greater than the threshold voltage ( $V_{TH}$ ) level.

- The application of a positive (+ve) gate voltage to a n-type eMOSFET attracts more electrons towards the oxide layer around the gate thereby increasing or enhancing the thickness of the channel allowing more current to flow.

- The reverse is true for the p-channel enhancement MOS transistor. The

application of a negative (-ve) gate voltage to the p-type eMOSFET enhances

the channels conductivity turning it "ON".

- The I-V Characteristic of n-channel enhancement MOS transistor is:

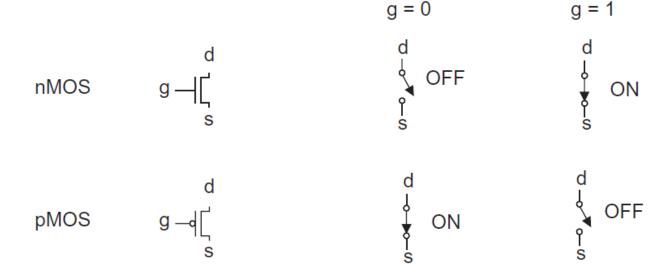

#### MOS transistors as switch

- nMOS

- In case of logical 0: open switch (does not conduct current)

- In case of logical 1: closed switch (conducts current)

- pMOS

- logical 0: conducts current,

- logical 1: does not conduct current

- The symbol of pMOS transistor has a circle at the gate terminal

# **Complementary Metal Oxide Semiconductor (CMOS)**

- Complementary MOS

- They consist of two types of MOSFETs: n-type and p-type

- Nowadays, logic circuits are CMOS.

- We have two complementary transistors:

- One conducts when the input logic level is high

- Other conducts when the input logic level is low

- We can create

- Inverters

- Basic logic gates (and, or, etc.)

- Complex logic gates

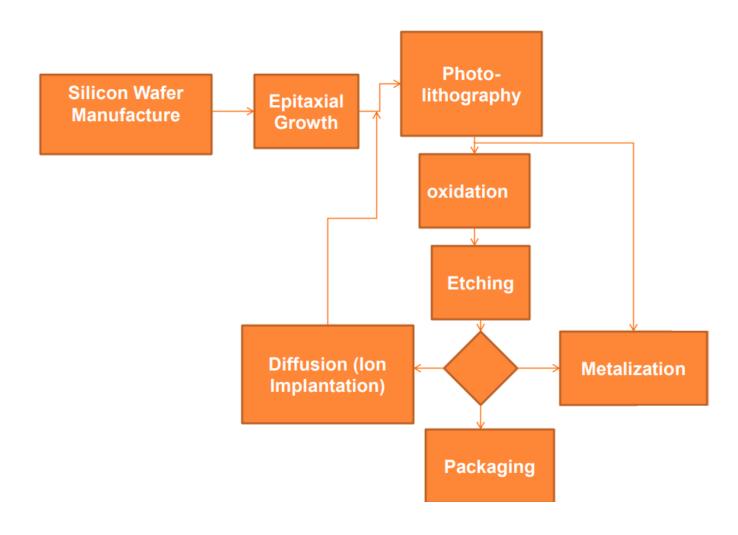

# **Fabrication Process Technologies**

# **Impurity Doping**

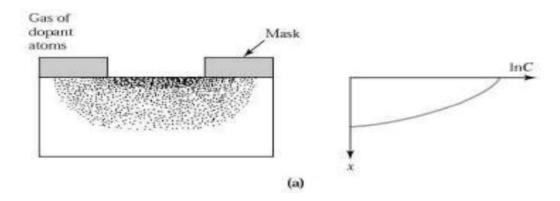

- Two methods for introducing impurities into Si to control the majority-carrier type and resistivity of layers.

- Diffusion: dopant atoms move from the surface into Si by thermal means via substitutional or interstitial diffusion mechanisms.

• Ion implantation: dopant atoms are forcefully added into Si in the form of energetic ion beam injection. Thermal Annealing is required.

# What Annealing

- Is the process of heating a metal or alloy to an appropriate temperature for a certain period of time and then slowly cooling (generally with the furnace cooling). The annealing can

- Decrease the number of lattice imperfection/distortion (e.g. after ion implantation, after oxide growth).

- Activate dopant atoms after implantation (atoms diffuse into vacancies from substitutional positions).

- Decrease residual stress in deposited layers and improve adhesion.

**Before Annealing**

**After Annealing**

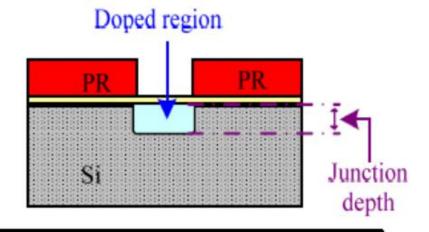

# **Doping Techniques Comparison**

# Diffusion

- High temperature, hard mask (SiO<sub>2</sub>)

- Isotropic dopant profile

- Cannot independently control the dopant concentration, junction depth

# Doped region SiO<sub>2</sub> SiO<sub>2</sub> Si

# Ion Implantation

- ◆Low temperature, PR mask

- Anisotropic dopant profile

- Can independently control the dopant concentration, junction depth

# **Doping Profile**

#### **Diffusion**

#### **Ion Implantation**

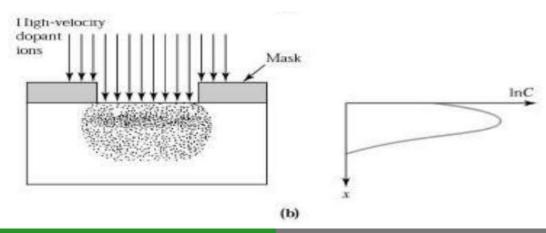

# Wafer growth – Czochralski Method (Cz)

The Cz process is the most common for large wafer diameter production.

- The puller consists of three main components:

- A furnace, which includes a fused-silica crucible, a graphite susceptor, a rotation mechanism (clockwise), a heating element, and a power supply.

- 2. A crystal-pulling mechanism, which includes a seed holder and a rotation mechanism (counter-Clockwise.

- 3. An ambient control, which includes a gas source, a flow control and an exhaust system.

- Pull rate, melt temperature and rotation rate are all important control parameters.

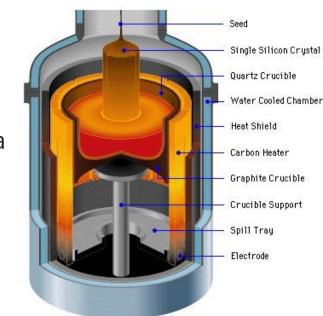

# Layer Growth and Deposition

- Chemical Vapour Deposition (CVD) is a chemical process used to produce high purity, high performance solid materials.

- In a typical CVD process, the substrate is exposed to one or more volatile precursors which react and decompose on the substrate surface to produce the desired deposit.

- There are other methods of layer growth and deposition as Physical vapour deposition (PVD), electroless plating, electro plating, Screen printing and Inkjet printing.

#### The Steps Involved in CVD

- 1. Transport of reactants by forced convection to the deposition region.

- 2. Transport of reactants by diffusion from the main gas stream to the wafer surface.

- 3. Adsorption of reactants on the wafer surface.

- 4. Surface processes, including chemical decomposition or reaction, surface migration, site incorporation, and other surface reactions.

- 5. Desorption of by-products from the surface.

- 6. Transport of by-products by diffusion back to the main gas stream.

7. Transport of by-products by forced convection away from the deposition region.

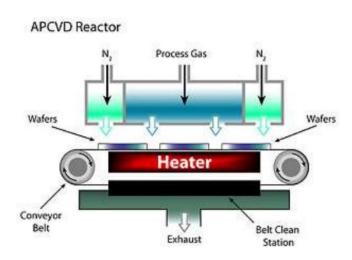

# Types of CVD

- CVD's are classified into two types on the basis of Operating Pressure.

- 1. Atmospheric Pressure CVD- APCVD

- HIGH TEMPERATURE process is used to deposit Silicon and compound films or hard metallurgical coatings like Titanium Carbide and Titanium Nitride.

- LOW TEMPERATURE process is used to deposit many insulating film layers such as Silicon dioxide for effective deposition.

#### 2. Low Pressure CVD.

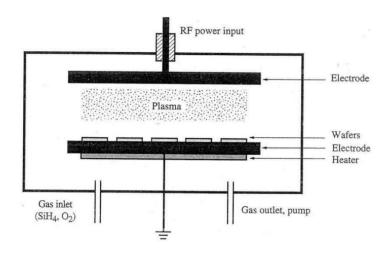

- Plasma Enhanced CVD (PECVD).

- PECVD is a process used to deposit thin films from a gas state (vapor) to a solid state on a substrate.

- Chemical reactions are involved in the process, which occur after creation of a plasma of the reacting gases.

- The helping hand of the Plasma helps in increasing the film quality at low temperature and pressure.

- Photochemical Vapour Deposition.

- Al thin films are deposited via photochemical vapour deposition on catalytic layers of Ti using dimethyl aluminum hydride.

- Deposition is carried out at low gas pressures to induce a surface reaction.

#### Thermal CVD

- In thermal CVD process, temperatures as high as 2000 degree Celsius is needed to deposit the compounds.

- There are two basic types of reactors for thermal CVD.

- 1. Hot wall reactor

- 2. Cold wall reactor

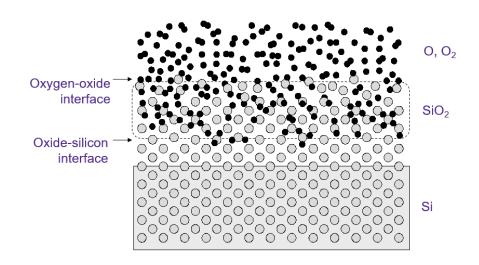

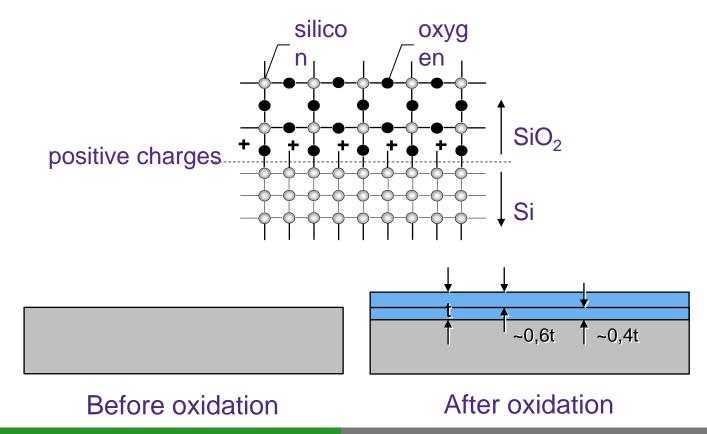

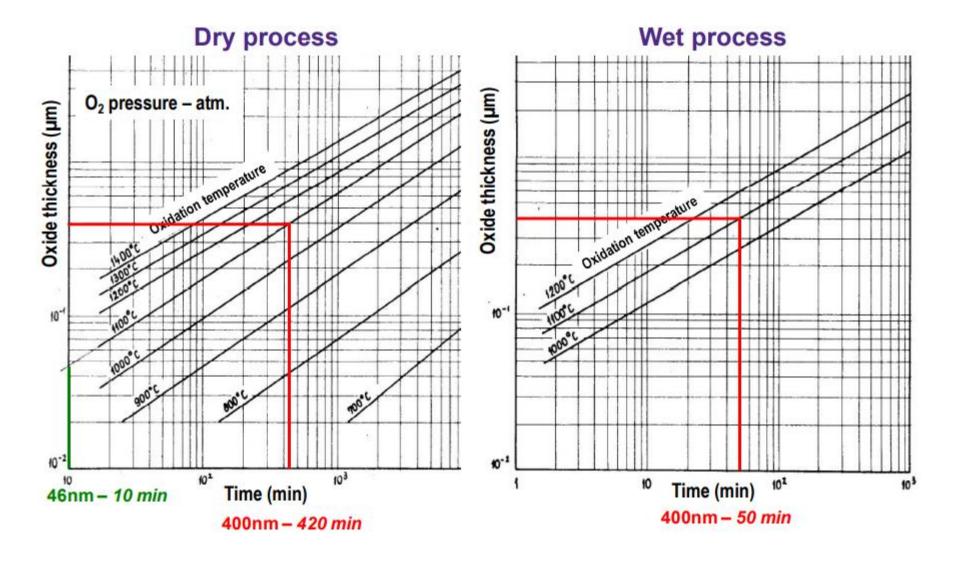

#### Oxidation

- Oxide is frequently employed as an insulator between two layers of metallization. Oxidation occurs when pure silicon (Si) is exposed to oxygen forming silicon dioxide (SiO<sub>2</sub>).

- SiO<sub>2</sub> growth is a key process step in manufacturing all Si devices as it creates extremely high electronic quality gate oxides.

- Characteristics of SIO<sub>2</sub>

- SiO<sub>2</sub> is stable down to 10<sup>-9</sup> Torr, T > 900°C.

- SiO<sub>2</sub> can be etched with HF which leaves Si unaffected.

- SiO<sub>2</sub> is a diffusion barrier for B, P, As.

- SiO<sub>2</sub> is good insulator, r > 10<sup>16</sup> ohm-cm.

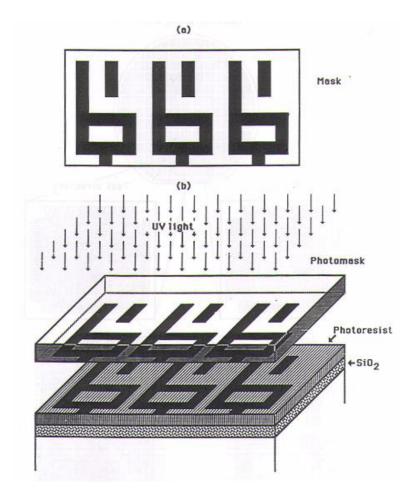

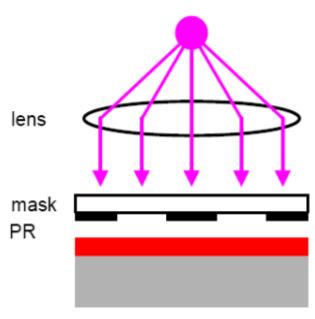

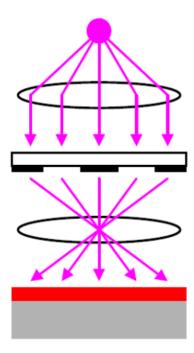

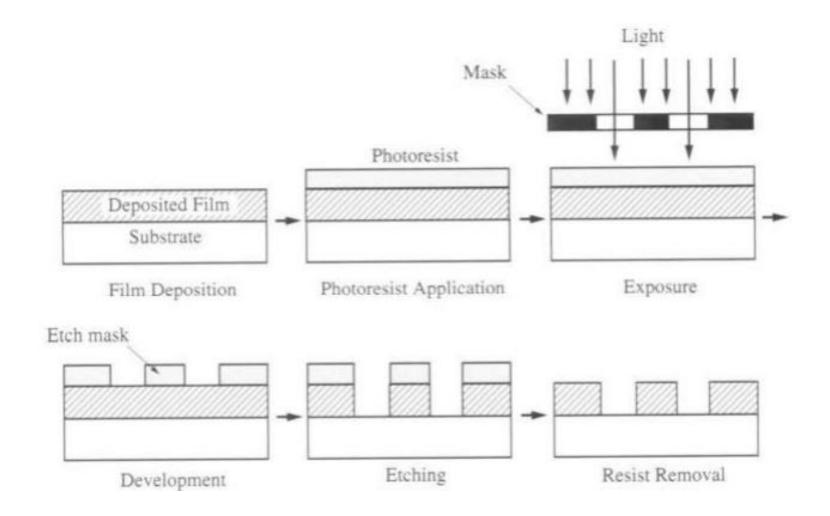

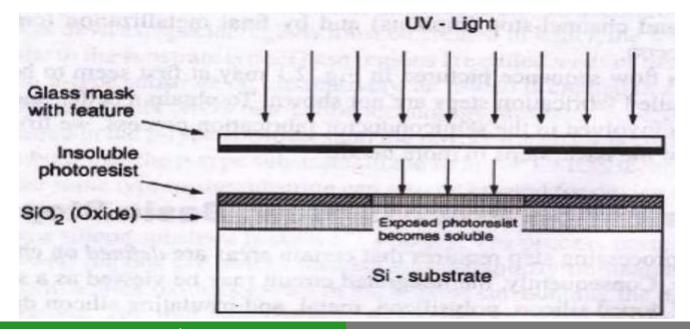

# Lithography

- Lithography is the most complicated, expensive, and critical process of modern IC manufacturing.

- Lithography transforms complex circuit diagrams into pattern which are define on the wafer to form a number of superimposed layers of insulator, conductor and semiconductors materials.

- The minimum feature size i.e., the minimum line width or line to line separation that can be printed on the surface, control the number of circuits that can be placed on the chip and has a direct impact on circuit speed. The evolution of IC is therefore closely linked to the evolution of lithographic tools.

A special agent called a photoresist is deposited on the surface. The photoresist is exposed to light through a mask, it changes its properties in a pattern.

# Basic Steps of the Advanced Technology

Trackstepper integrate d system Wafer clean

- Pre-bake and primer coating

- Photoresist spin coating

- Soft bake

- Alignment and exposure

- Post exposure bake

- Development

- Hard bake

- Pattern inspection

PR coating

Development

1) Dehydration

2) Resist spin-on

3) Softbake

4) Alignment and exposure

5) Post-Exposure Bake (depending on resist)

6) Development

7) Hardbake (depending on resist and application)

8) Verification of the developed structure

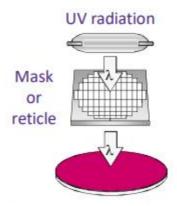

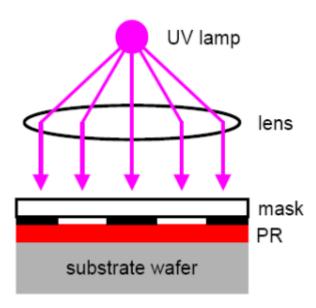

# Mask Alignment & Exposure

- Contact Alignment: Resist is in contact with the mask, 1:1 magnification

- Advantages: Inexpensive equipment and moderately high resolution.

- Disadvantages: Contact with the mask degrades the mask (pinholes and scratches are created on the metal-oxide layers of the mask and particles or dirt are directly imaged in the wafer).

- Proximity Alignment: : Resist is almost, but not in contact with the mask, 1:1 magnification

- Advantages: Inexpensive equipment, low resolution (~1-2 um or slightly better) and Longer mask lifetime.

- Disadvantages: Diffraction effects limit accuracy of pattern transfer. Less repeatable than contact methods.

- Projection Alignment: Mask image is projected a distance from the mask and de-magnified to a smaller image, 1:4-1:10 magnification

- Advantages: Can be very high resolution (~0.007 um or slightly better), No mask contact results in almost no mask wear (high production compatible), mask defects or particles on mask are reduced in size on the wafer.

- Disadvantages: Extremely expensive and complicated equipment, diffraction effects limit accuracy of pattern transfer.

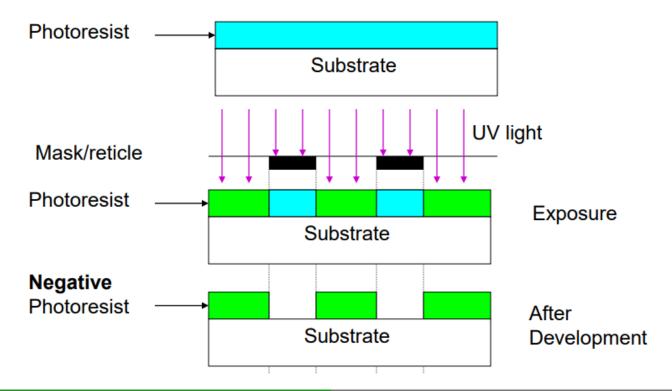

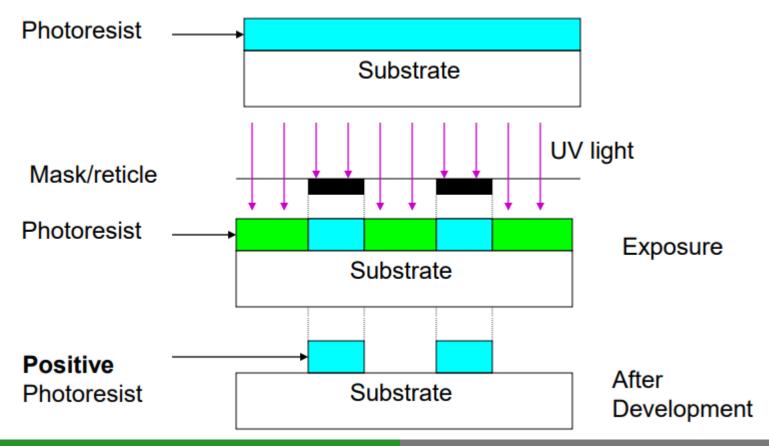

# Types of Photoresist

- Negative Photoresist

- Becomes insoluble after exposure

- When developed, the unexposed parts dissolved.

- Cheaper

#### Positive Photoresist

- Becomes soluble after exposure

- When developed, the exposed parts dissolved

- Better resolution

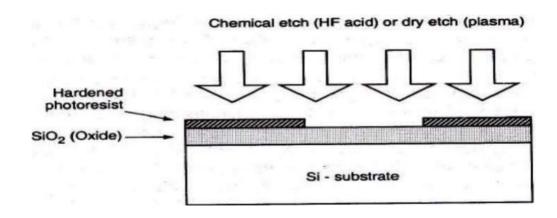

# **Etching**

- After a thin film is deposited, it is usually etched to remove unwanted materials and leave only the desired pattern on the wafer. The process is done many times.

- In addition to deposited films, sometimes we also need to etch the Si wafer to create trenches (especially in MEMS).

- The masking layer may be photoresist, SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>. The etch is usually done until another layer of a different material is reached

# **Etching Types**

- Etching can be done "wet" or "dry"

- Wet etching

- Uses liquid etchants

- Wafer is immersed in the liquid

- Process is mostly chemical

- Wet etching is not used much in VLSI wafer fabrication.

- Dry etching

- Uses gas phase etchants in a plasma

- The process is a combination of chemical and physical action.

- Process is often called "plasma etching".

- This is the normal process used in most VLSI fabrication.

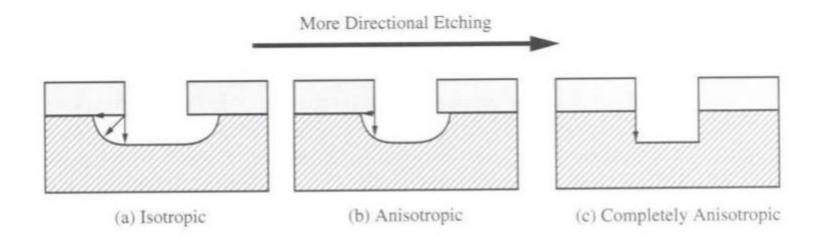

Etch directionality is a measure of the etch rate in different directions (usually vertical versus lateral)

- Uniform etching speed in all directions

- Under etching

- Different etching speed in different directions.

- Etching profile depends on the wafer orientation

#### **Circuit Environment**

# Budapest University of Technology and Economic Department of Electron Devices

## **Circuit Environment**

## Lecture 3

- Fabrication Processes

- Fabrication of MOSFET Transistor

- Fabrication of CMOS Transistor

**Ahmed I Alnahhal**

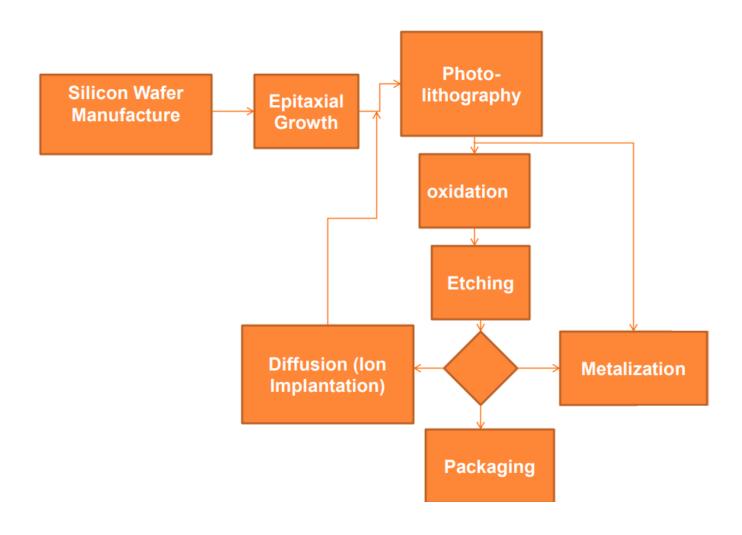

## **FABRICATION PROCESSES FOR VLSI DEVICES**

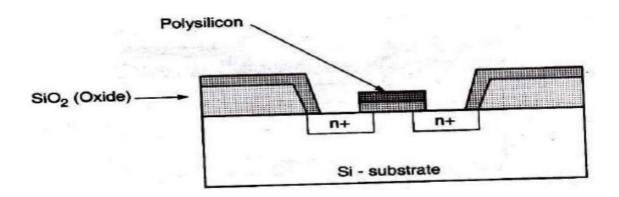

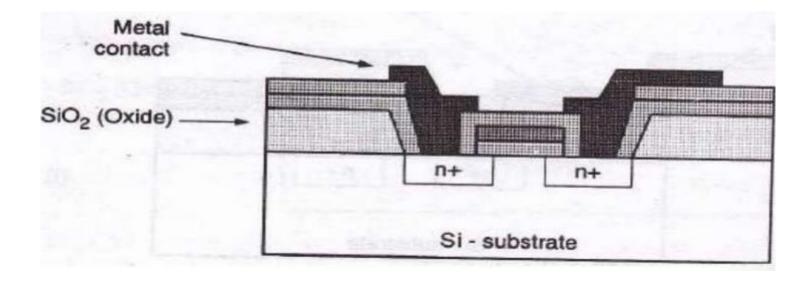

#### **Fabrication of MOSFET Transistor**

- Fabrication process sequence for NMOS

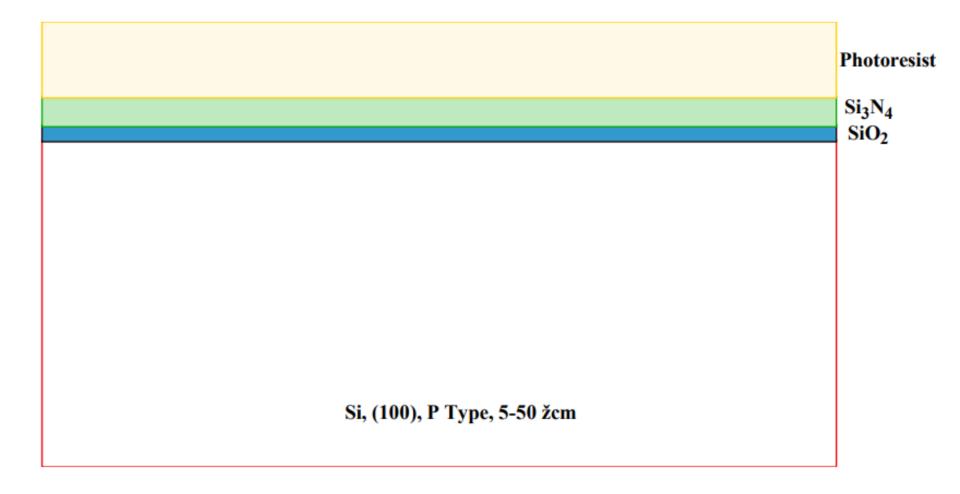

- 1. The starting Si wafer is a lightly doped p type substrate.

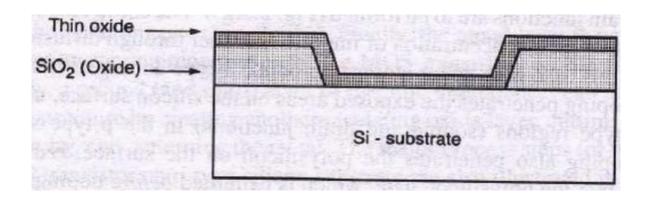

2. First step is to oxidize the Si to form a layer of SiO<sub>2</sub>

3. Coat the Si with photoresist.

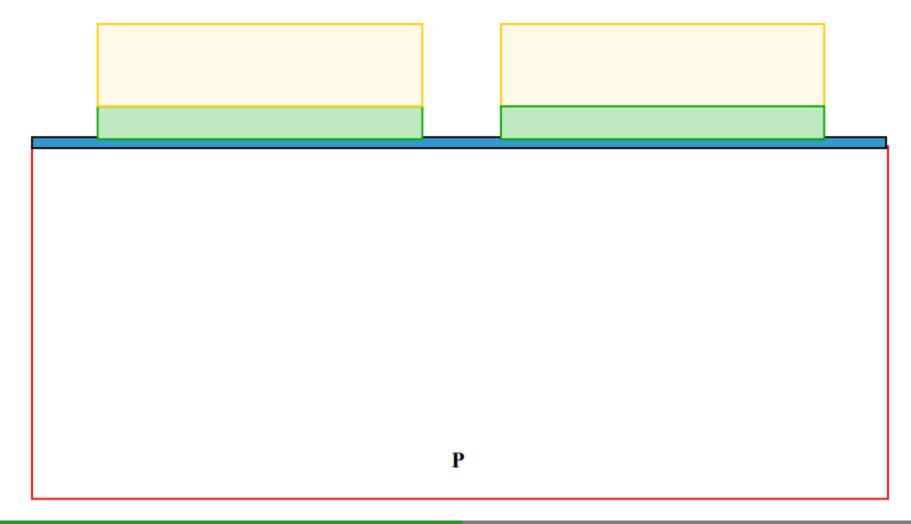

4. The next step is lithography in order to form source and drain regions.

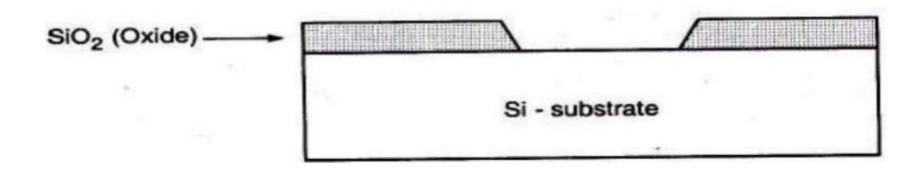

5. The SiO<sub>2</sub> regions which are not covered by hardened photoresist can be etched away either by chemical etching or dry etching.

6. The remaining photoresist can be removed by using another solvent.

7. Deposit a layer of thin oxide in order to form gate oxide of the NMOS transistor

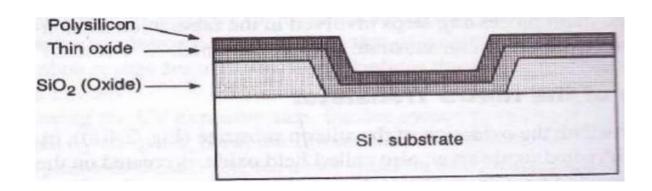

8. A layer of polysilicon is deposited. It is used as gate electrode material for MOS to interconnect it.

#### **Circuit Environment**

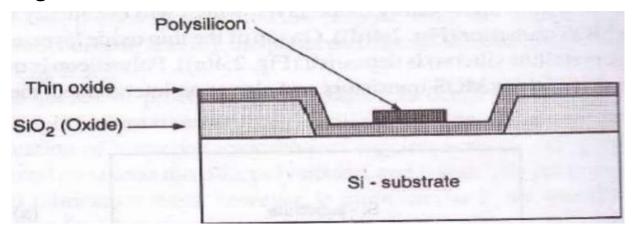

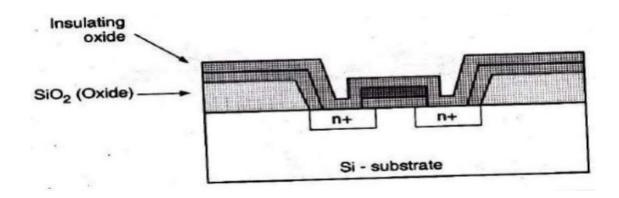

9. The polysilicon layer is patterned and etched to form the interconnects and the MOS transistor gate.

10. The thin oxide not covered by polysilicon is also etched away so that source and drain junctions may be formed.

11. The entire silicon surface is then doped with a high concentration of impurities either by diffusion or ion implantation.

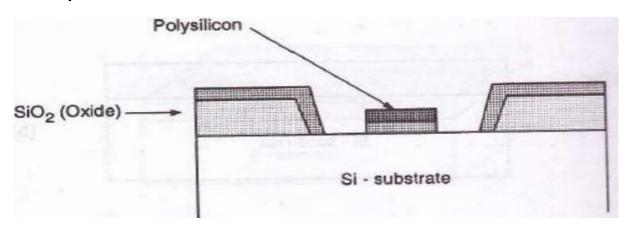

12. Once the source and drain regions are completed, the entire surface is again covered with and insulating layer of  $SiO_2$ .

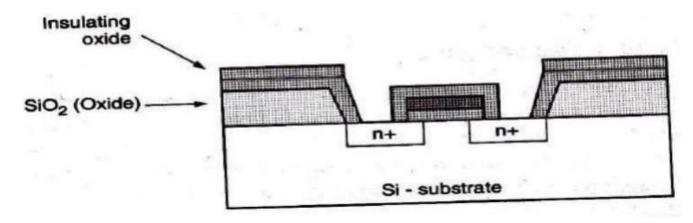

13. The insulating oxide is then patterned in order to provide contact window for drain and source junctions.

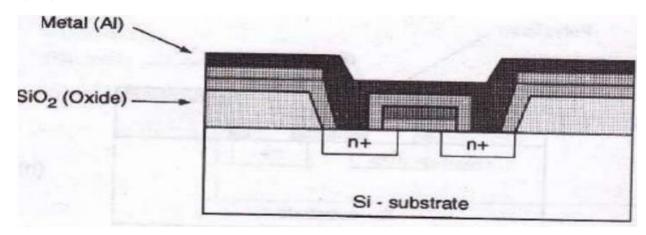

14. The surface is now covered with evaporated aluminium which will form the interconnections.

#### **Circuit Environment**

15. Finally the metal layer is patterned and etched, completing the interconnections of the MOS transistor on the surface.

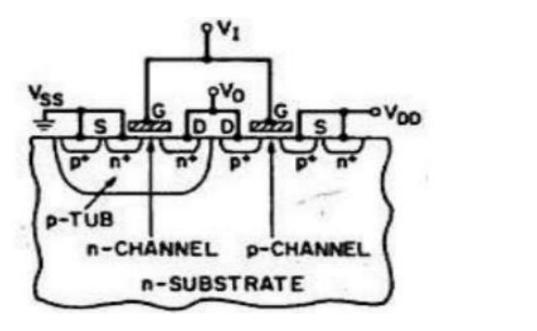

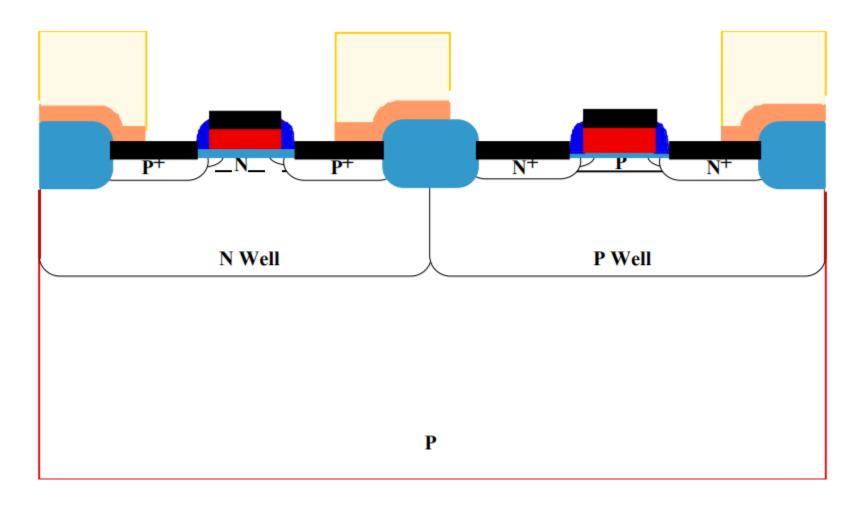

# **CMOS Transistor Technology**

- A CMOS inverter is realized by the series combination of a PMOS and NMOS transistors.

- The cross section of the inverter structure shows the n-channel transistor formed in a p-region called tub or well. The gates of the transistors are connected to from the input.

#### **Circuit Environment**

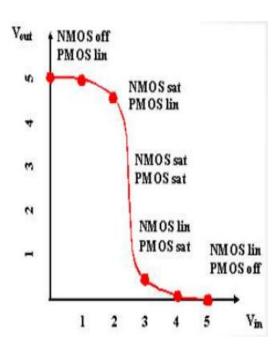

- Transfer characteristic of the CMOS inverter is output voltage as a function of input voltage.

- In order to understand the operation of the CMOS inverter, define the threshold voltages of NMOS and PMOS transistors. Let  $V_{Tn} = 1 \text{ V}$  &  $V_{Tn} = -1 \text{ V}$  and  $V_{DD} = 5 \text{ V}$ .

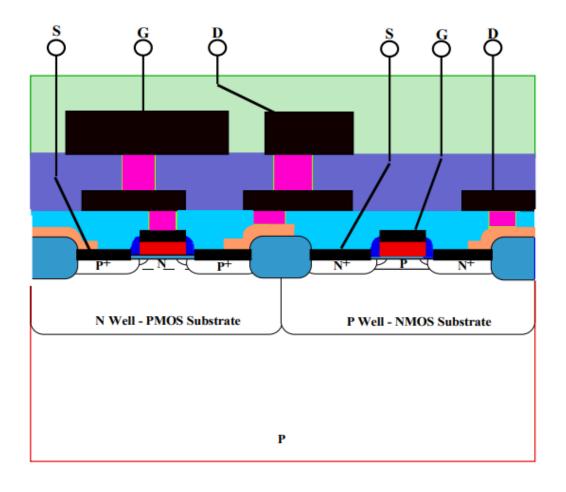

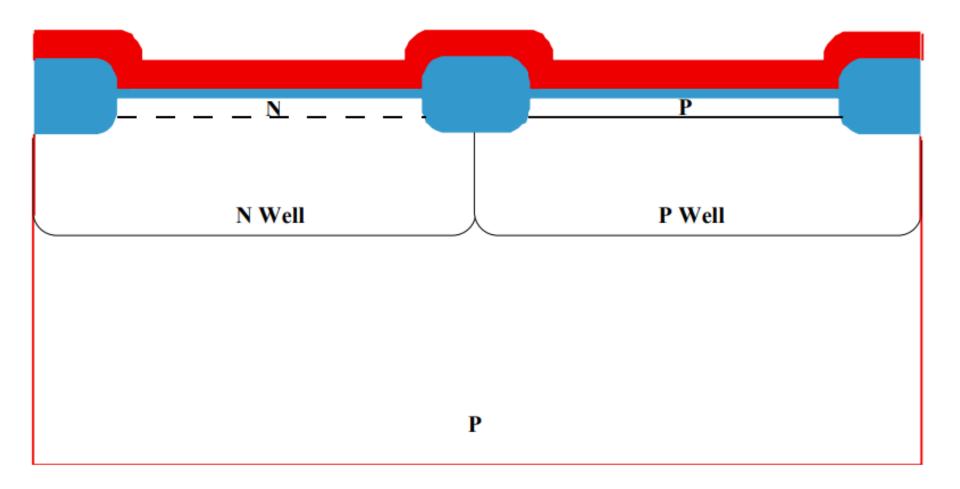

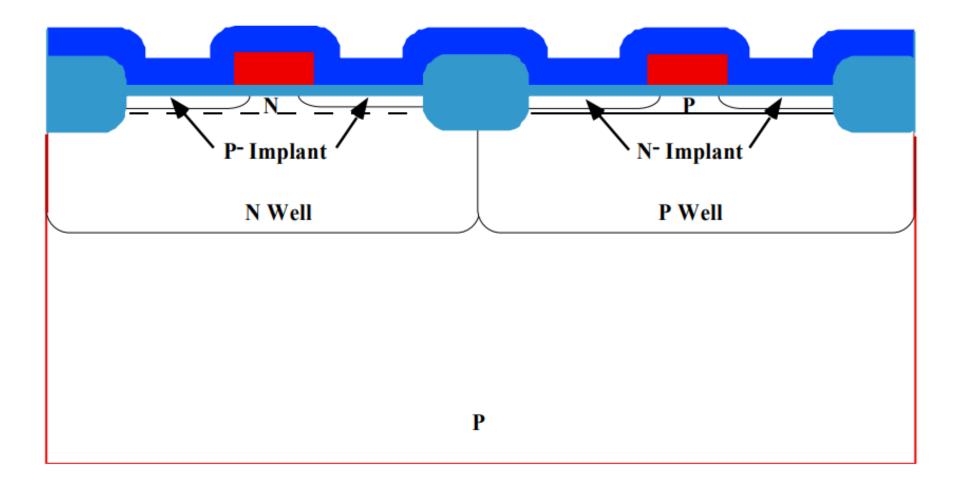

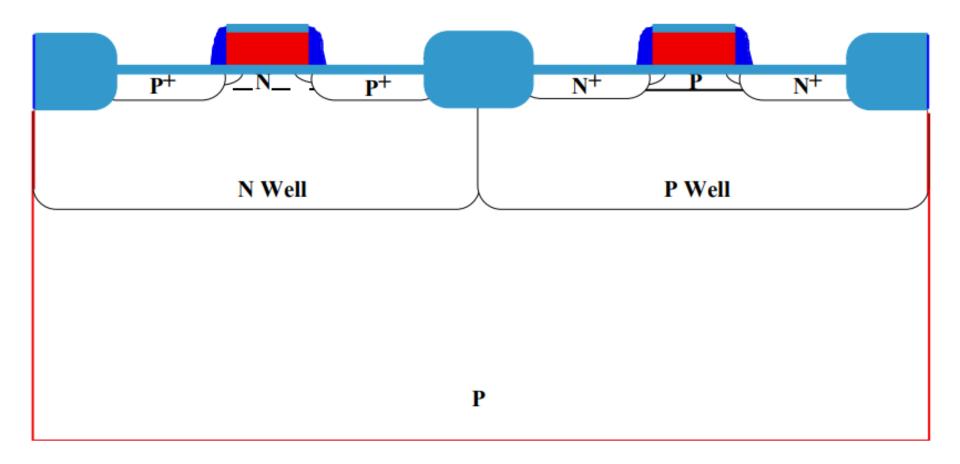

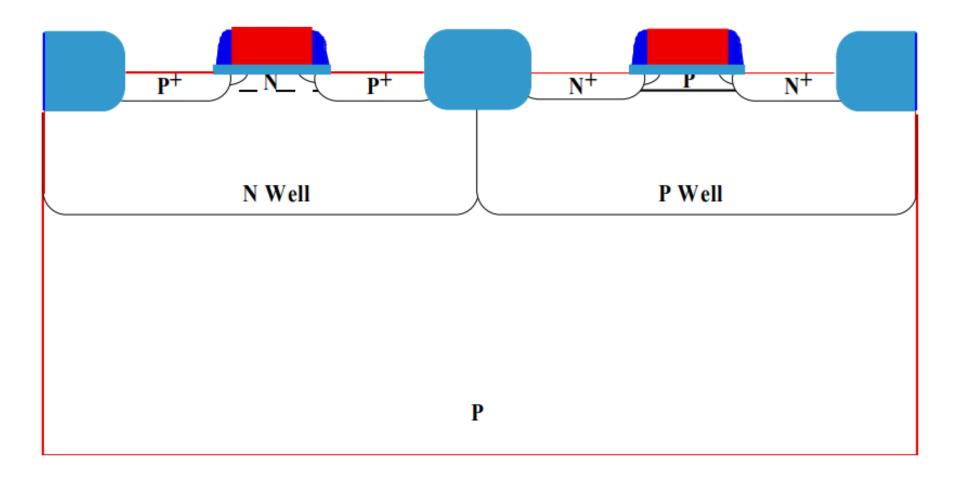

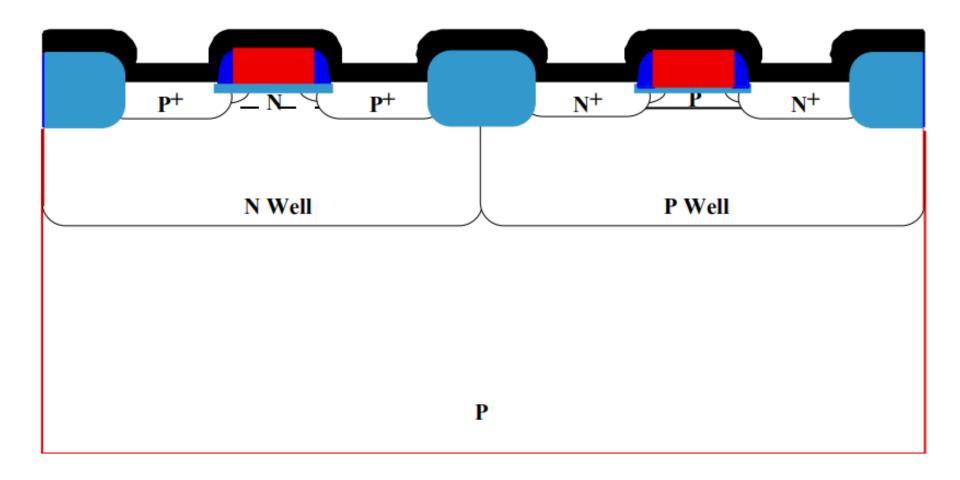

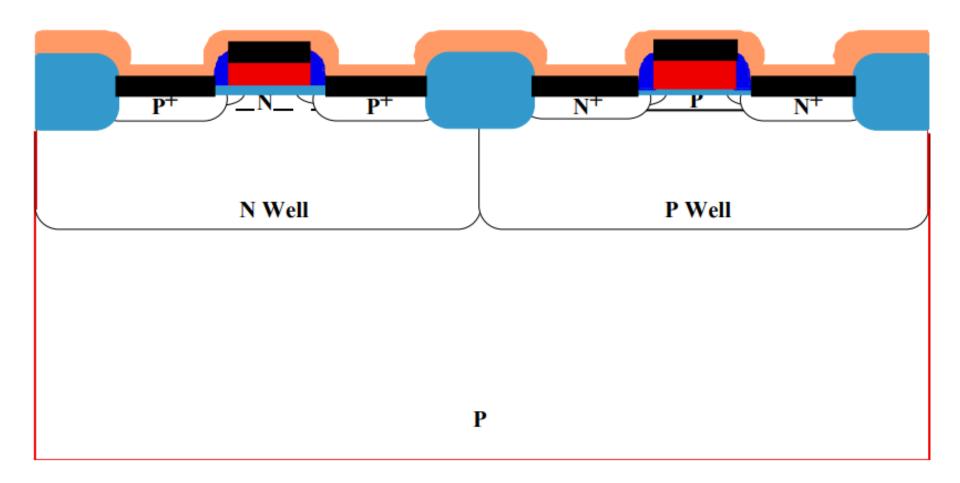

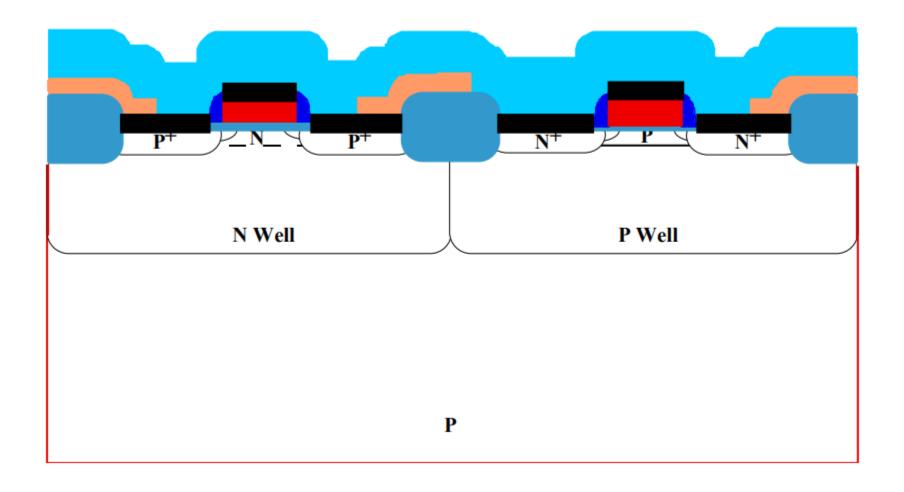

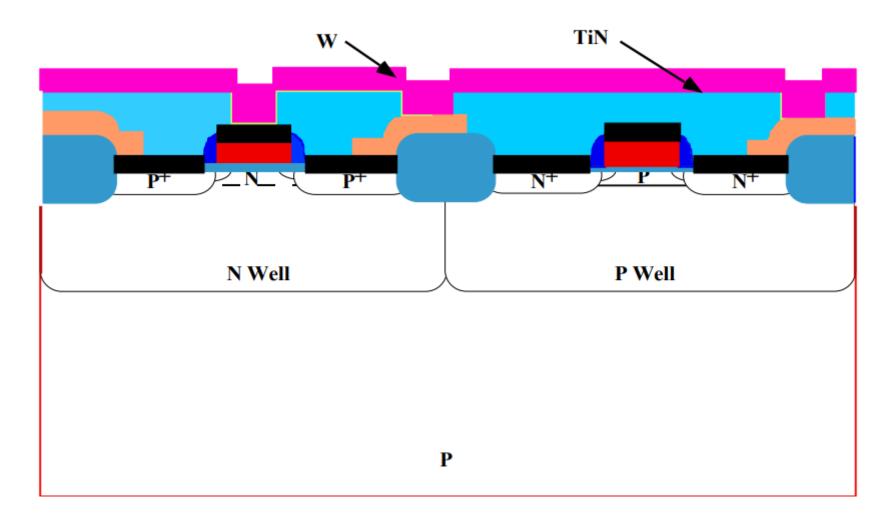

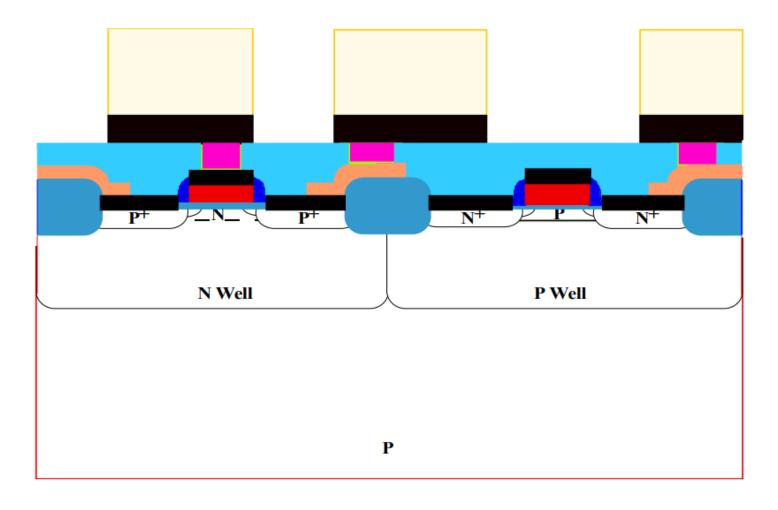

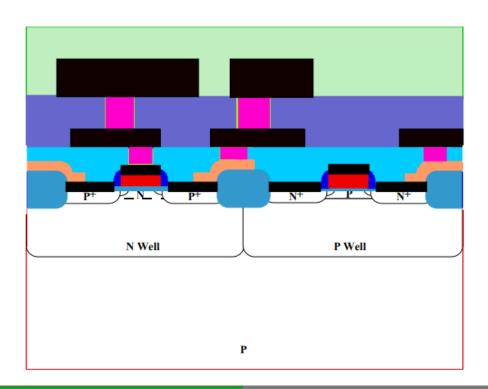

## **Fabrication of CMOS transistor**

## Cross sectional view of final CMOS circuits

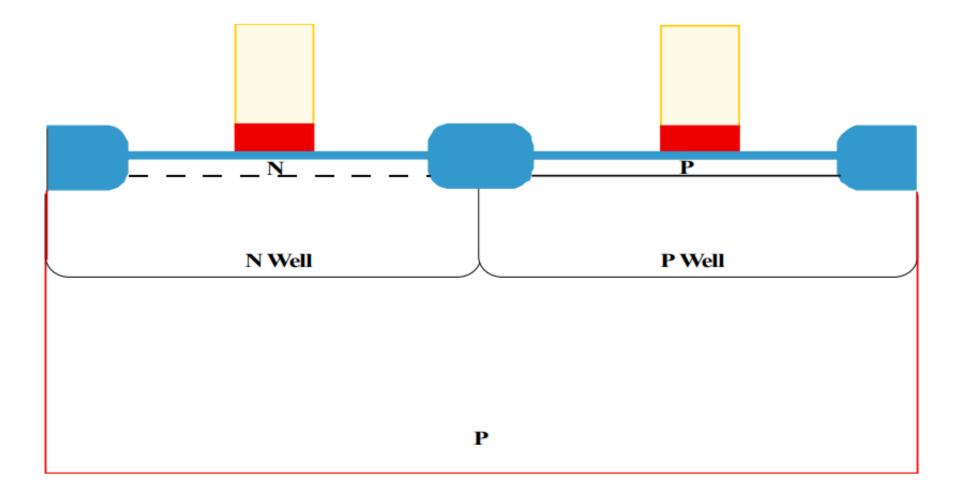

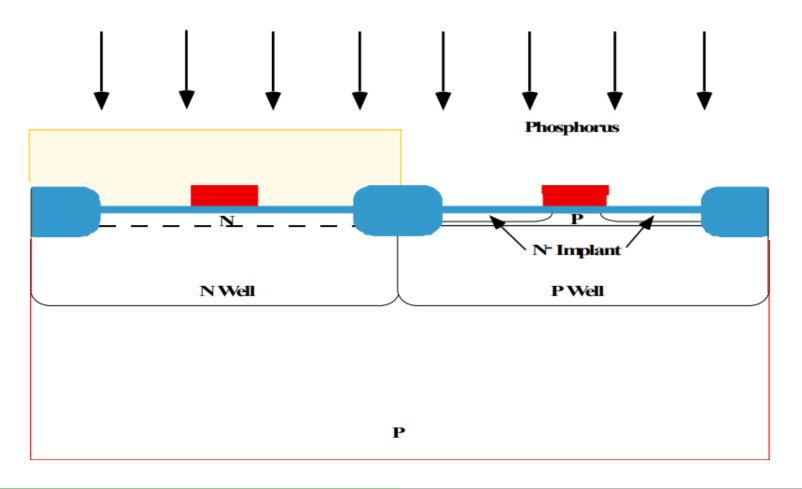

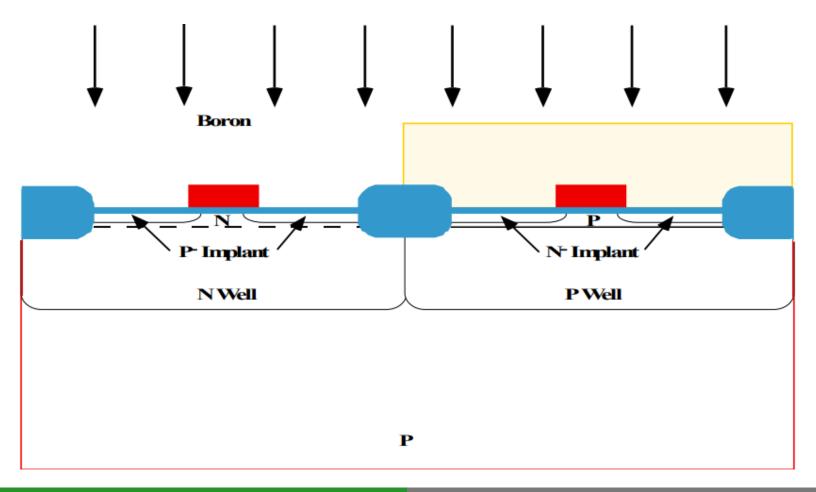

## **CMOS Process Flow**

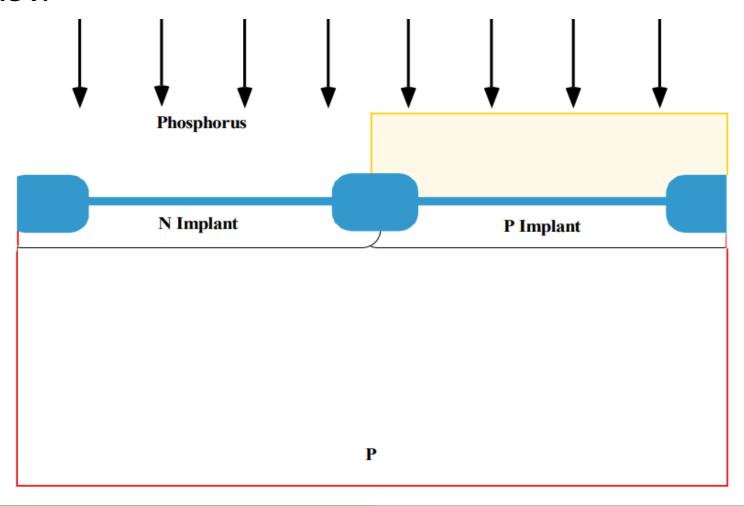

Mask #1 patterns the active areas. The nitride is dry etched.

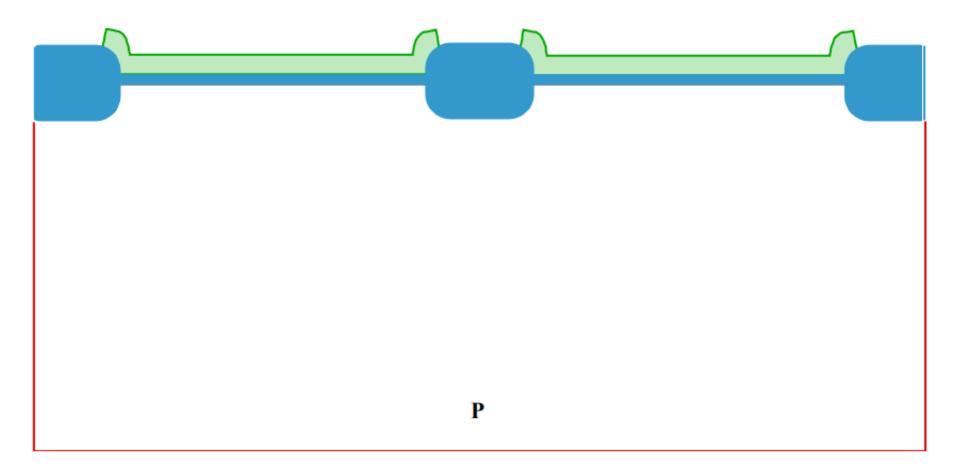

Field oxide is grown using a LOCOS process. Typically 90 min @ 1000 °C in  $H_2O$  grows  $\approx 0.5 \mu m$ .

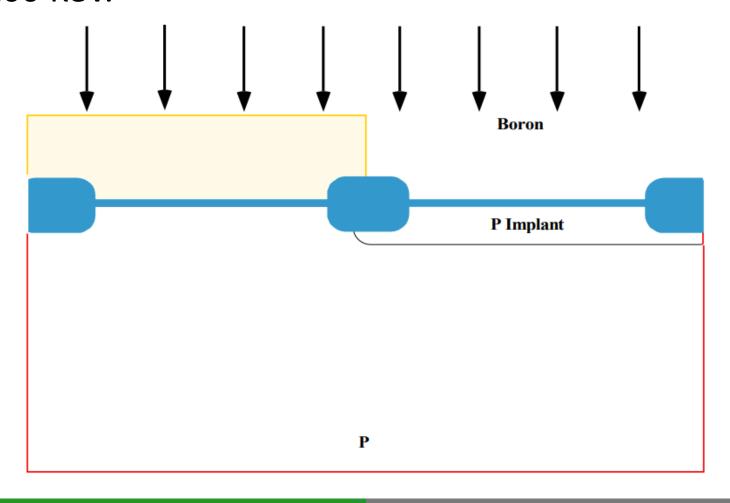

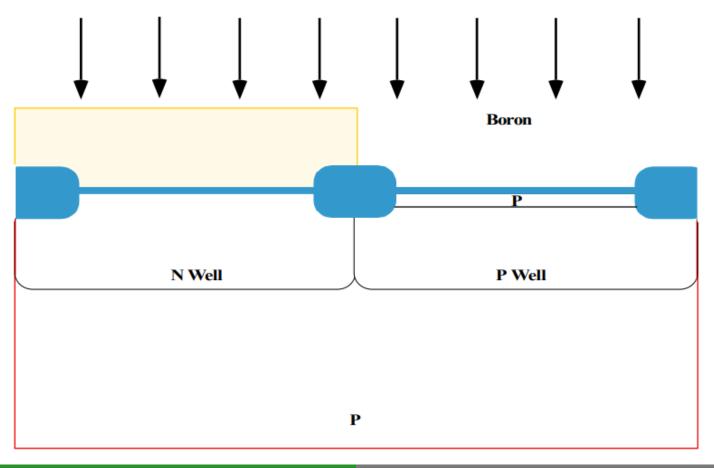

Mask #2 blocks a B<sup>+</sup> implant through the PMOS and just to form the wells for the NMOS devices. Typically, 10<sup>13</sup> cm<sup>-2</sup> @ 150-200 KeV.

Mask #3 blocks a  $P^+$  implant through the NMOS and just to form the wells for the PMOS devices. Typically,  $10^{13}$  cm<sup>-2</sup> @ 300 KeV.

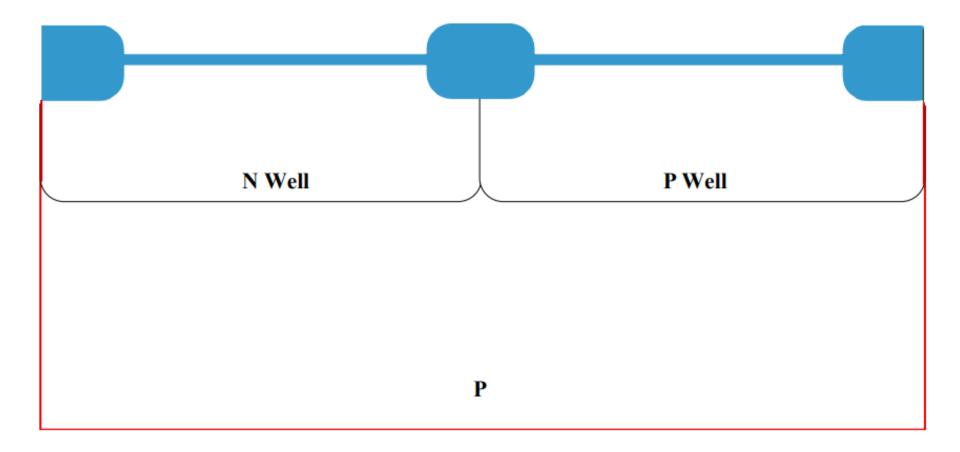

A high temperature drive-in produces the "final" well depths and repairs implant damage. Typically, 4-6 hours @ 1000 °C - 1100 °C.

Mask #4 is used to mask the PMOS devices. A  $V_{TH}$  adjust implant is done on the NMOS devices, typically a 1-5 x  $10^{12}$  cm<sup>-2</sup> B+ implant @ 50 - 75 KeV.

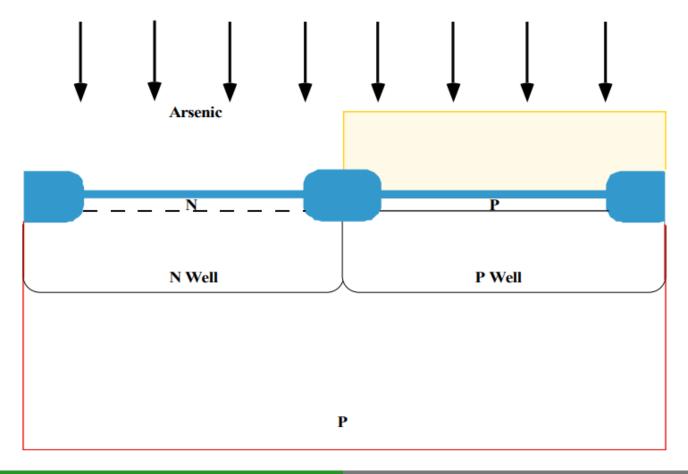

Mask #5 is used to mask the NMOS devices. A  $V_{TH}$  adjust implant is done on the PMOS devices, typically 1-5 x  $10^{12}$  cm<sup>-2</sup> As+ implant @ 75 - 100 KeV.

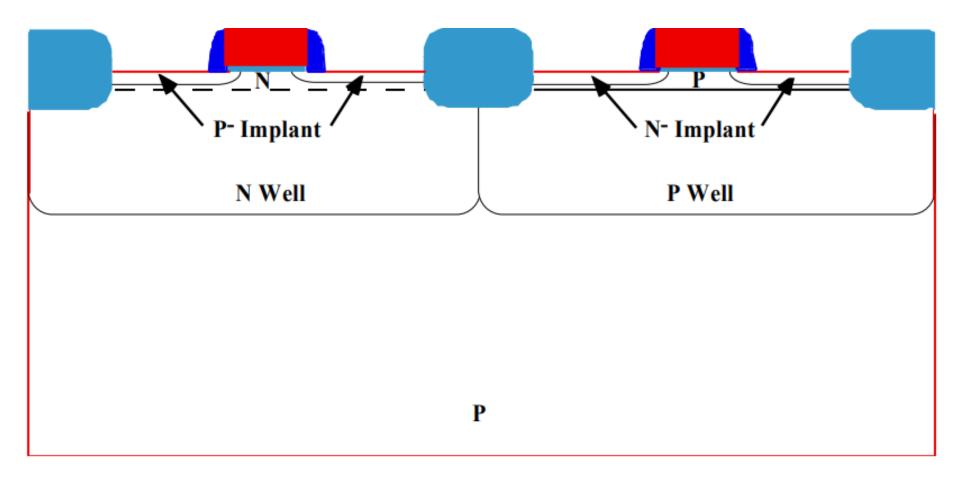

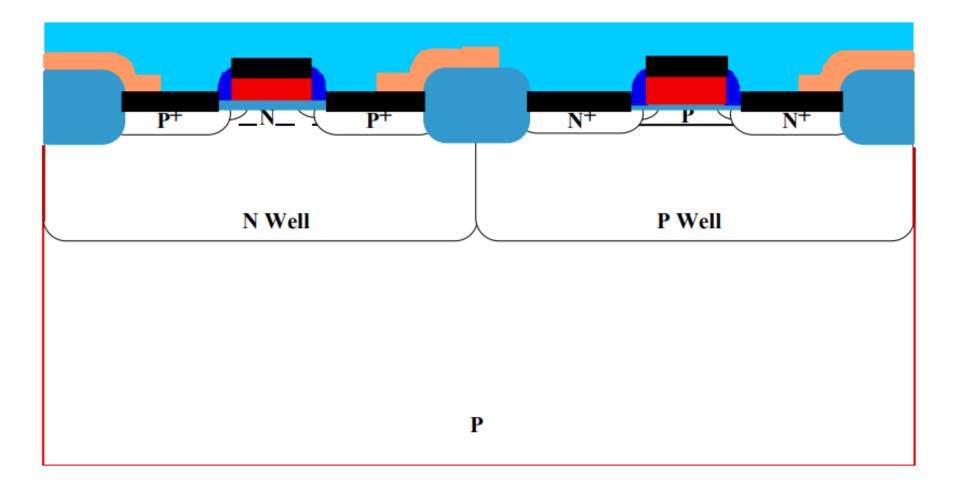

Polysilicon is deposited by LPCVD (  $\approx 0.5 \mu m$ ). An unmasked P<sup>+</sup> or As<sup>+</sup> implant dopes the poly (typically 5 x  $10^{15}$  cm<sup>-2</sup>).

Mask #6 is used to protect the MOS gates. The poly is plasma etched using an anisotropic etch.

Mask #7 protects the PMOS devices. A P<sup>+</sup> implant forms the LDD regions in the NMOS devices (typically 5 x  $10^{13}$  cm<sup>-2</sup> @ 50 KeV).

Mask #8 protects the NMOS devices. A B<sup>+</sup> implant forms the LDD regions in the PMOS devices (typically 5 x  $10^{13}$  cm<sup>-2</sup> @ 50 KeV).

Conformal layer of  $SiO_2$  is deposited (typically 0.5 µm).

Anisotropic etching leaves "sidewall spacers" along the edges of the poly gates.

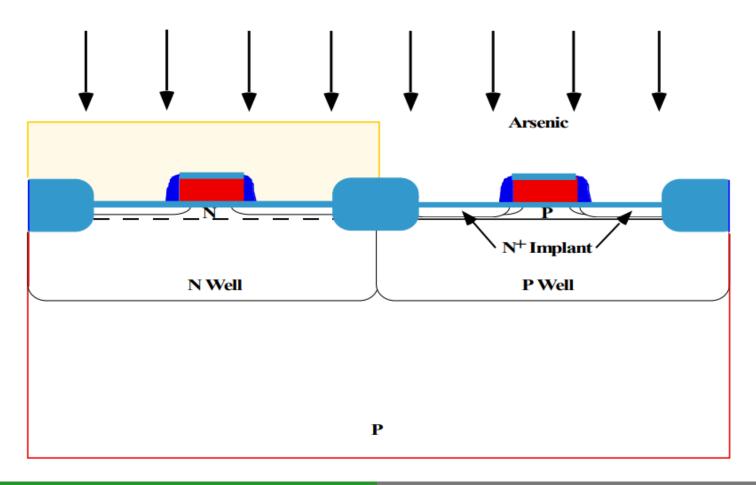

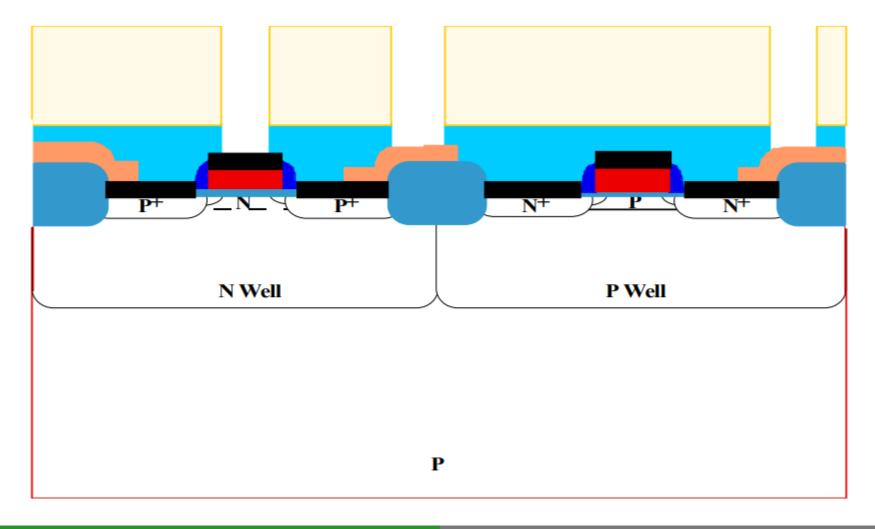

Mask #9 protects the PMOS devices, An As<sup>+</sup> implant forms the NMOS source and drain regions (typically 2-4 x 10<sup>15</sup> cm<sup>-2</sup> @ 75 KeV).

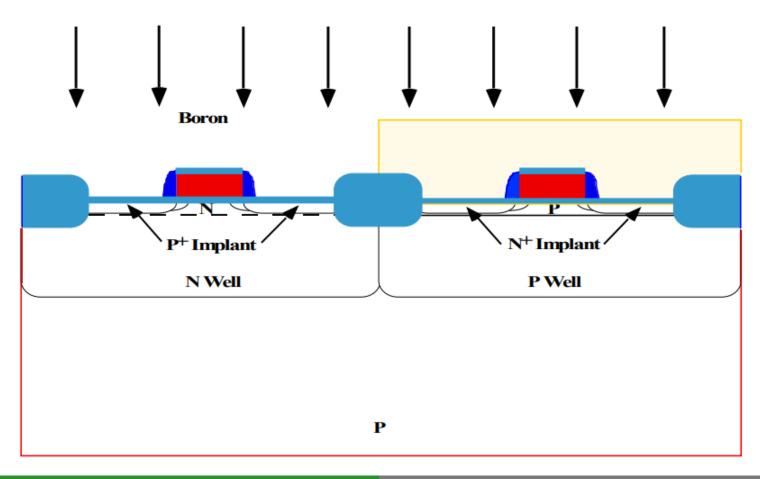

Mask #10 protects the NMOS devices, A B<sup>+</sup> implant forms the PMOS source and drain regions (typically 1-3 x  $10^{15}$  cm<sup>-2</sup> @ 50 KeV).

A final high temperature anneal drives-in the junctions and repairs implant damage (typically 30 min @ 900°C or 1 min @ 1000°C.

An unmasked oxide etch allows contacts to Si and poly regions.

Ti is deposited by sputtering (typically 100 nm).

The Ti is reacted in an  $N_2$  ambient, forming TiSi<sub>2</sub> and TiN (typically 1 min @ 600 - 700 °C).

Mask #11 is used to etch the TiN, forming local interconnects.

A conformal layer of  $SiO_2$  is deposited by LPCVD (typically 1  $\mu$ m).

CMP is used to planarize the wafer surface.

Mask #12 is used to define the contact holes. The  $SiO_2$  is etched.

A thin TiN barrier layer is deposited by sputtering (typically a few tens of nm). followed by W CVD deposition.

Al is deposited on the wafer by sputtering. Mask #13 is used to pattern the Al and plasma etching is used to etch it.

Intermetal dielectric and second level metal are deposited and defined in the same way as level #1. Mask #14 is used to define contact vias and Mask #15 is used to define metal 2. A final passivation layer of Si<sub>3</sub>N<sub>4</sub> is deposited by PECVD and patterned with Mask #16.

## Budapest University of Technology and Economic Department of Electron Devices

## **Circuit Environment**

## Lecture 4

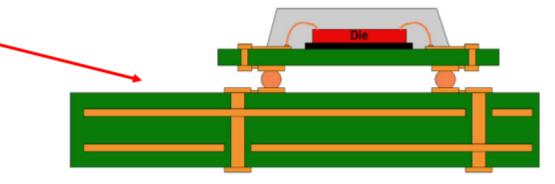

# Introduction to the Integrated Circuits Packaging

## **Packaging Definition**

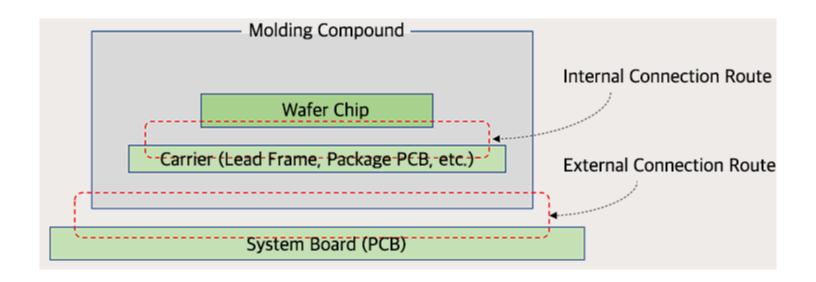

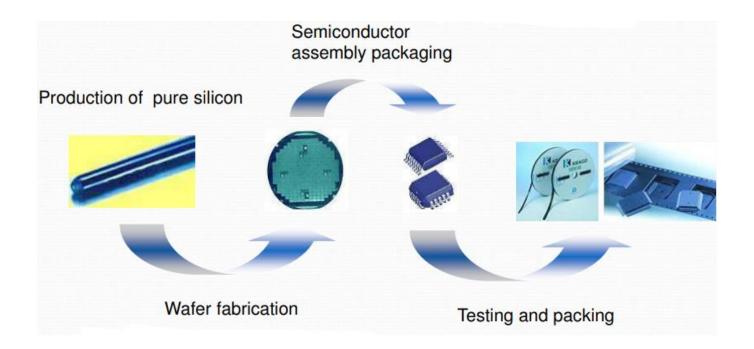

- Integrated circuit packaging is the final stage of semiconductor device fabrication, in which the block of semiconductor material is encapsulated in a supporting case that prevents physical damage and corrosion.

- The case, known as a "package", also supports the electrical contacts which connect the device to a circuit board.

- In the integrated circuit industry, the process is often referred to as packaging. Other names include semiconductor device assembly, assembly, encapsulation or sealing.

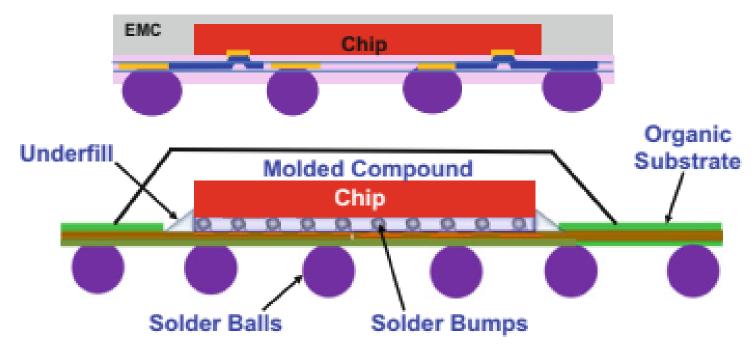

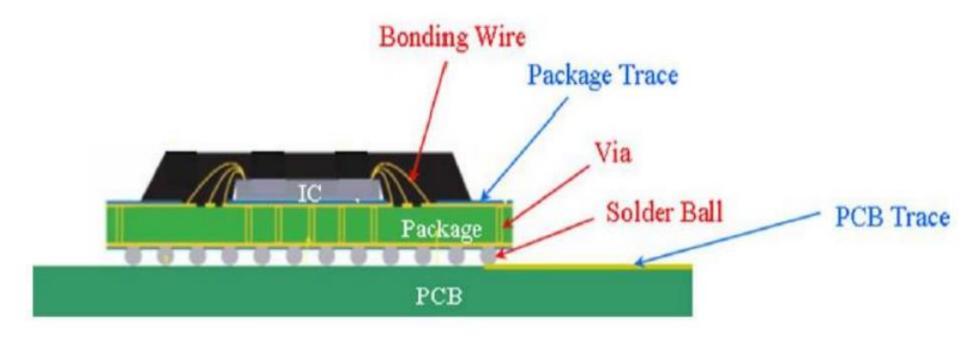

The semiconductor packaging consists of a semiconductor chip, a carrier (package PCB, lead frame, etc.) on which the chip is placed, and a molding compound which surrounds them.

The internal and external connection were previously made with lines (wires or lead frames). Recently, points (bumpers or balls) are typically being used.

- Meanwhile, molding compounds play an important role in taking out the heat inside and protecting the chip from external damage.

- The packaging stage is followed by testing of the integrated circuit.

## **Needs of Packaging**

- The IC packaging has many functions. These functions include:

- Environmental protection is needed to prevent chemical damage that would be detrimental to the IC performance.

- Mechanical stability and thermal management are both required to increase the reliability and lifetime of the IC by preventing physical damage.

- Electrical connections must be made between the package and the IC to enable interaction with a larger system on a circuit board.

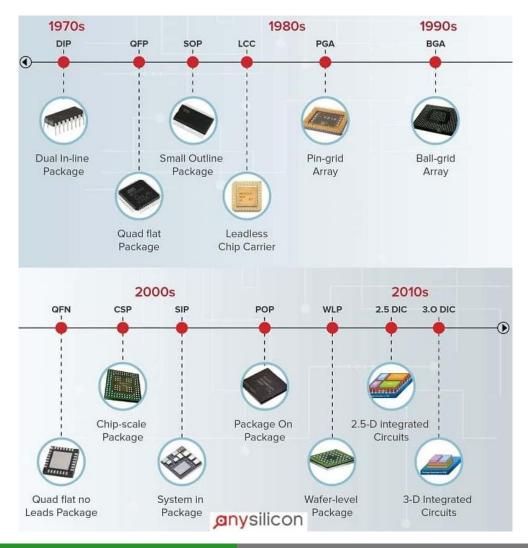

## **Packaging History**

## **IC Packaging Phases**

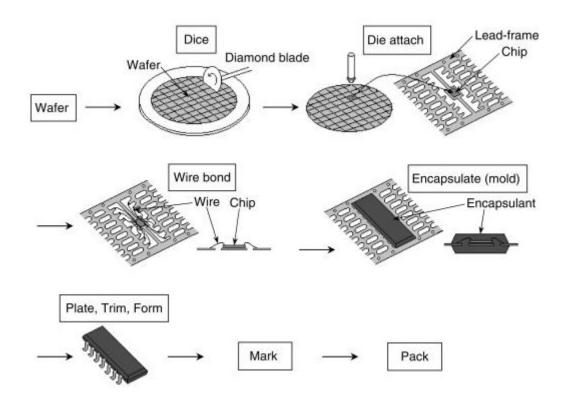

The main operations performed are Die attaching, IC bonding, and IC encapsulation.

#### 1. Die attachment

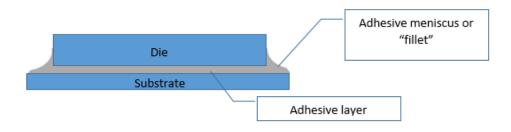

- Die attachment is the process of attaching the silicon chip to the die pad or die cavity of the support structure (e.g. lead frame) of the semiconductor package.

- There are two common die attach processes

- Adhesive die attach

- ➤ It uses adhesives such as **polyimide**, **epoxy** and **silver-filled glass** as die attach material to mount the die on the die pad or cavity.

- The mass of epoxy climbing the edges of the die is known as the die attach fillet. Excessive die attach fillet may lead to die attach contamination of the die surface. Too little of it may lead to die lifting or die cracking.

- ➤ Die attach films or tapes can also be employed instead of adhesives but they are less easy to apply and requiring more substantial equipment expenditure.

- >UV adhesives offer another method of attaching dies but due to shadow areas underneath the die or wafer can't be cured with UV light alone, a secondary cure method such as a thermal cure is required.

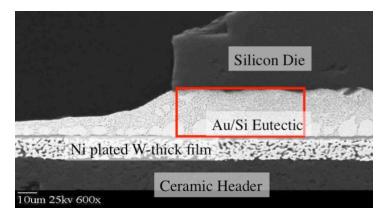

- Eutectic die attach.

- It uses a **eutectic alloy** to attach the die to the cavity. A eutectic alloy is an alloy with the lowest melting point possible for the metals combined in the alloy.

- The Au-Si eutectic alloy is the most used die attach alloy in semiconductor packaging.

- Both processes use special die attach equipment and die attach tools to mount the die.

- The presence of voids in the die attach material affects the quality and reliability of the device itself.

- Large die attach voids result in low shear strength and low thermal/electrical conductivity and produce large die stresses that may lead to die cracking.

- Small voids provide sufficient shear strength and electrical/thermal conductivity, while 'cushioning' large dice from stresses.

- Total absence of voids may mean high strength, but it may also induce large dice to crack. The strength of die attachment is measured using the die shear test.

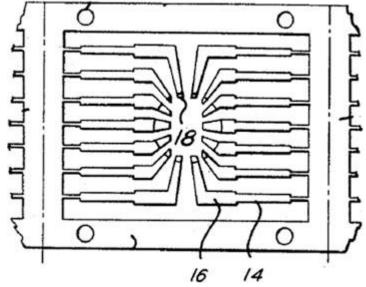

#### 2. Wire Bonding

- Wire bonding, is the process of providing electrical connection between the silicon chip and the external leads of the semiconductor device using very fine bonding wires.

- The wire used in wire bonding is usually made either of gold (Au) or aluminium (Al), although Cu wire bonding is starting to gain a foothold in the semiconductor manufacturing industry.

- There are two common wire bonding processes

- Au ball bonding

- Al wedge bonding

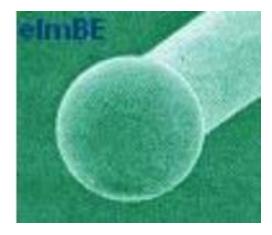

#### Au ball bonding

A gold ball is first formed by melting the end of the wire through electronic flame-off process (EFO).

- ➤ This free-air ball has a diameter ranging from 1.5 to 2.5 times the wire diameter. Free air ball size consistency, controlled by the EFO, and the tail length is critical in good bonding.

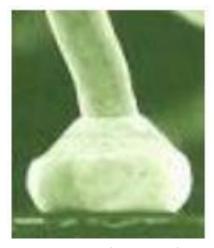

- Adequate amounts of pressure, heat, and ultrasonic forces are then applied to the ball for a specific amount of time, forming the initial metallurgical weld between the ball and the bond pad.

- The wire is then run to the corresponding finger of the leadframe, forming a gradual arc or "loop" between the bond pad and the leadfinger.

- ➤ Pressure and ultrasonic forces are applied to the wire to form the second bond (known as a wedge bond.

- Al wedge bonding

- > A clamped aluminium wire is brought in contact with the aluminium bond pad.

- ➤ Ultrasonic energy is then applied to the wire for a specific duration while being held down by a specific amount of force, forming the first wedge bond between the wire and the bond pad.

- ➤ The wire is then run to the corresponding lead finger, against which it is again pressed.

- The second bond is again formed by applying ultrasonic energy to the wire. The wire is then broken off by clamping and movement of the wire.

- Gold ball bonding is much faster than aluminum wedge bonding, which is why it is extensively used in plastic packaging.

- Unfortunately, gold ball bonding on Al bond pads can not be used in hermetic packages, primarily because the high sealing temperatures (400-450 deg C) used for these packages tremendously accelerate the formation of Au-Al intermetallic that can lead to early life failures

#### 3. IC Encapsulation

- After wire bonding, it is important to protect the IC package by applying molded encapsulation.

- Encapsulation provides an economical way to protect device packages by:

- Isolating the active devices from environmental pollutants.

- Offering mechanical protection.

- A commonly used process is transfer molding, in which high temperature and pressure forced through a mold chase over the die and die frame and into the cavity on the frame where the die was placed earlier. The hardened epoxy forms the body of the final package.

- Controlling time, pressure, and flow are critical issues in the encapsulation step.

- Miscalculations can cause several problems such as wire sweep (wires pushed together causing a short circuit within the component), or partial molding and mold voiding, which are pockets (or bubbles) that form in the mold during the process.

- Another die-protecting option is ceramic packaging. In ceramic packages, instead of a molded cover, a cap of either ceramic or metal is welded or sealed over the die, encasing it in a sealed environment.

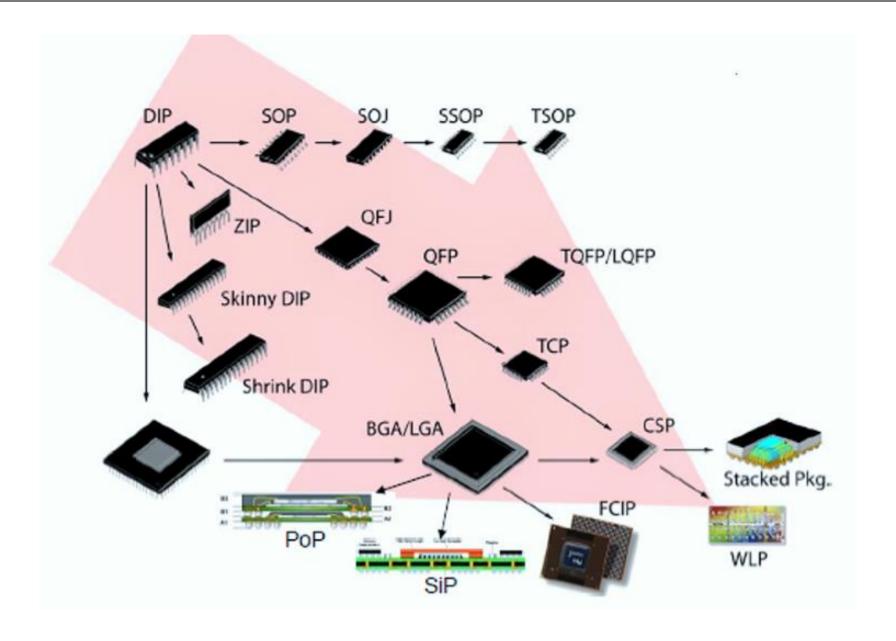

## **Package Type & Trend**

## Packages being categorized in few ways

- Type of substrate used

- Chip configuration / arrangement

- Type of interconnection

- Type of protection

- Package grouping based on its characteristic

- Type of board mounting

- Type of electronic packaging levels

- Type of substrate used

- Metal Can, Lead frame, Ceramic, PCB, Flexible / laminated / tape and Bare die

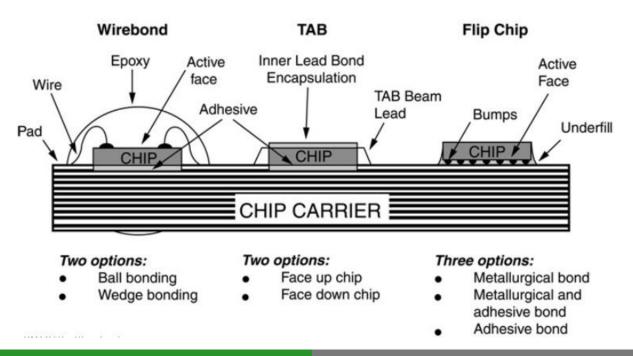

- Type of interconnection (The process of creating the interconnection between the die of an IC with lead).

- Wire bonding

- Bridge

- Tape Automated Bonding (TAB)

- Flip chip

- Direct Chip Attachment (DCA)

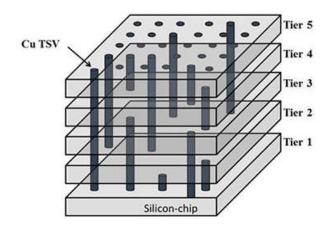

- Through-silicon via (TSV)

- o Its is a vertical electrical connection that passes completely through a silicon wafer or die.

- o TSVs are high-performance interconnect techniques used as an alternative to wirebond and flip chips to create 3D packages and 3D integrated circuits.

## Type of protection

- Metal Can

- Plastic/Ceramic Covered

- Singulated Molding

- Mold array process MAP

- Wafer level

- Package grouping based on its characteristic

- Optical

- Sensor

- I/O Card

- Hermetic

- Type of board mounting

- Through-Hole Mount Packages

- Surface Mount Packaging

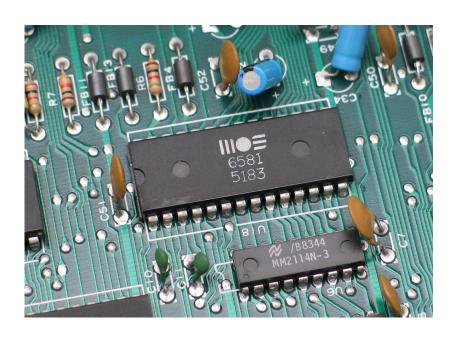

## **Through-Hole Mount Packages**

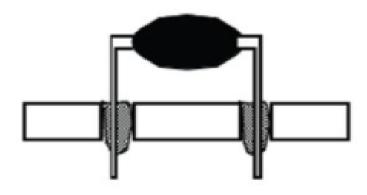

They are designed in a way that the lead pins are stuck through one side of the board and soldered on the other.

- They are bigger in size as compared to the other kind. These are majorly used in electronic equipment to compensate for the board space and cost limitations.

- Through-hole mount packages come in ceramic and plastic types. The package varies in size due to the difference in the number of pins in different packages.

- These pins are placed in a manner that they can be adjusted on to the centre of a breadboard without short-circuiting each other or even get soldered into PCBs.

## Through-Hole Mount Package types

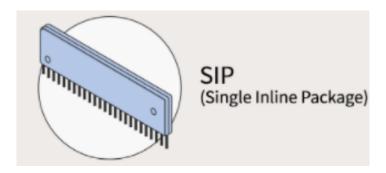

A Single Inline Package (SIP) is a computer chip package that contains only a single row of connection pins.

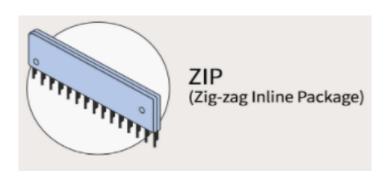

• Zig-zag Inline Package (ZIP) was a short-lived packaging technology for integrated circuits, particularly dynamic RAM chips. It was intended as a replacement for Dual Inline Package (DIP).

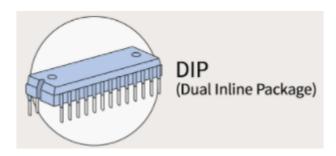

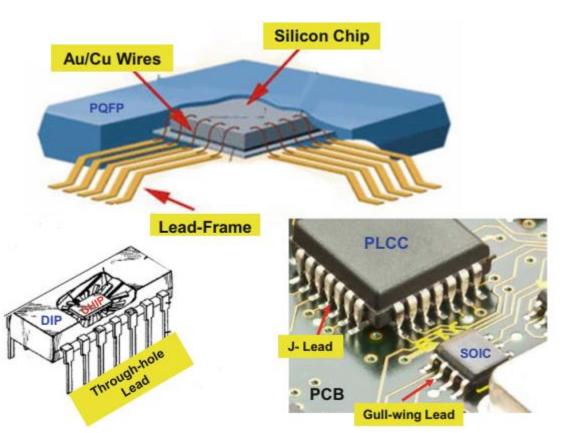

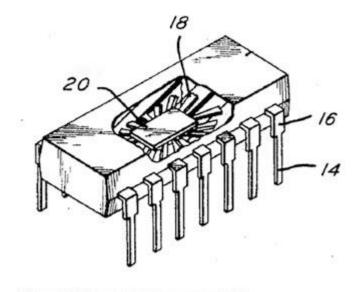

Dual Inline Package (DIP) is an electronic component package with a rectangular housing and two parallel rows of electrical connecting pins.

- There are many types of DIP Packages, Plastic Dual In-Line Package (PDIP) and Molded Dual In-Line Package (MDIP) are the few popular types.

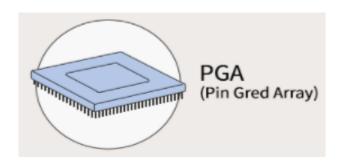

- Pin Grid Array (PGA) is square or rectangular, and the pins are arranged in a regular array on the underside of the package.

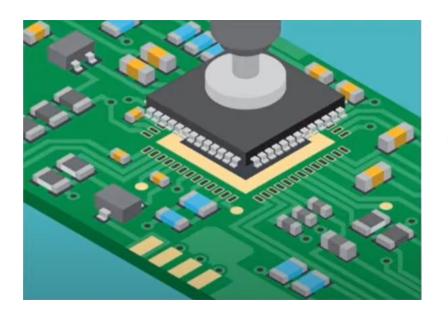

# **Surface Mount Packaging**

The leads do not pass-through holes in the PCB. Instead, surface mount package leads are aligned to electrical contacts on the PCB and are connected simultaneously by solder reflow.

- Surface mount packaging follows the technology of mounting or placing the components directly on the printed circuit board surface. Although this process of fabrication helps do things quickly, it also increases the chances of defects.

- This is because of the miniaturization of components and also because they are mounted extremely close to each other.

- This, in turn, results in making it extremely important to detect the failure in the entire process. Again, Surface mount packaging also uses ceramic or plastic molding.

# Surface Mount Package types

- Single Side

- Surface Vertical-Mount (SVP)

- Dual Side

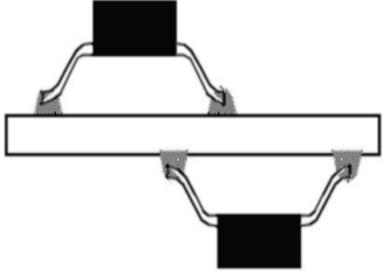

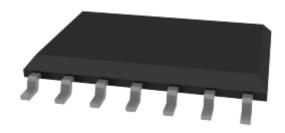

- Small Outline Package (SOP) packages are characterized by gull-wing type leads are drawn from each package body in two directions and can be mounted flat.

Thin-Small Outline Package (TSOP). They are very low-profile (about 1 mm) and have tight lead spacing (as low as 0.5 mm).

Small Outline J-lead Package (SOJ) is a version of SOP with J-type leads instead of gull-wing leads.

# Quadruple Side

Quad Flat Package (QFP) is a surface mount integrated circuit package with "gull wing" leads extending from each of the four sides.

Quad Flat J-lead Package (QFJ) are characterized by J-shaped leads which are drawn out from each package body in four directions and can be mounted flat.

Leadless Chip Carrier (LCC) has no "leads", but instead has rounded pins through the edges of the ceramic or molded plastic package.

Leadless Chip Carrier, Small Outline J-lead Package (LCC SOJ)

#### Full Surface

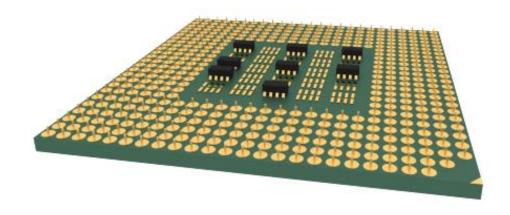

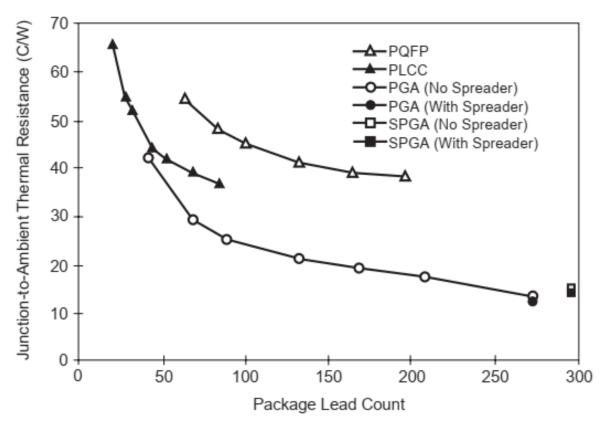

Ball Grid Array (BGA) is a type of surface-mount packaging (a chip carrier) used for integrated circuits. BGA packages are used to permanently mount devices such as microprocessors.

- Most packages can be made using ceramic or plastic. The integrated circuits are hermetically sealed for protection from the environment. The pins can be on one side (single inline or zigzag pattern of leads), two sides (dual inline package or DIP), or four sides of the package (quad package).

- Most advanced packages have leads distributed over a large portion of the surface of the package as in through-hole pin grid arrays (PGAs) or surface-mounted ball grid arrays (BGAs).

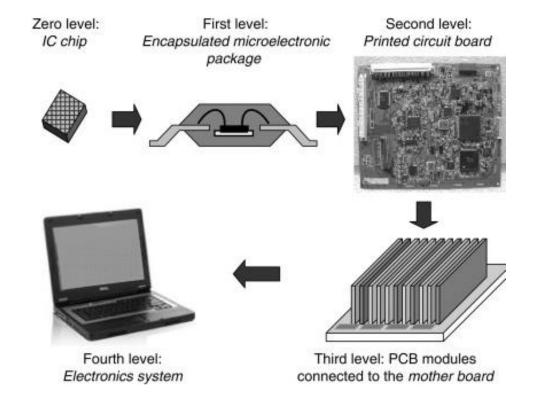

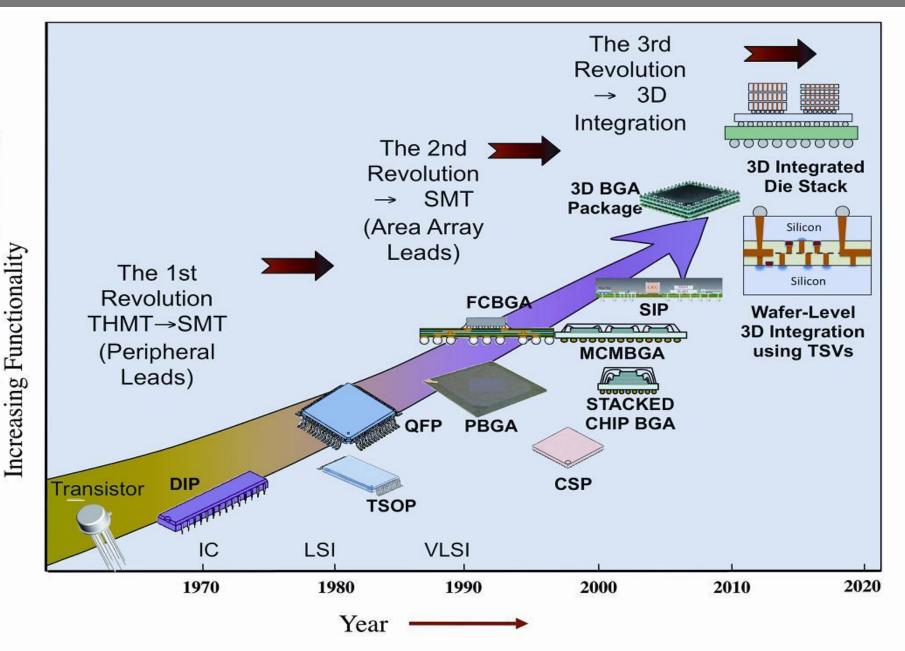

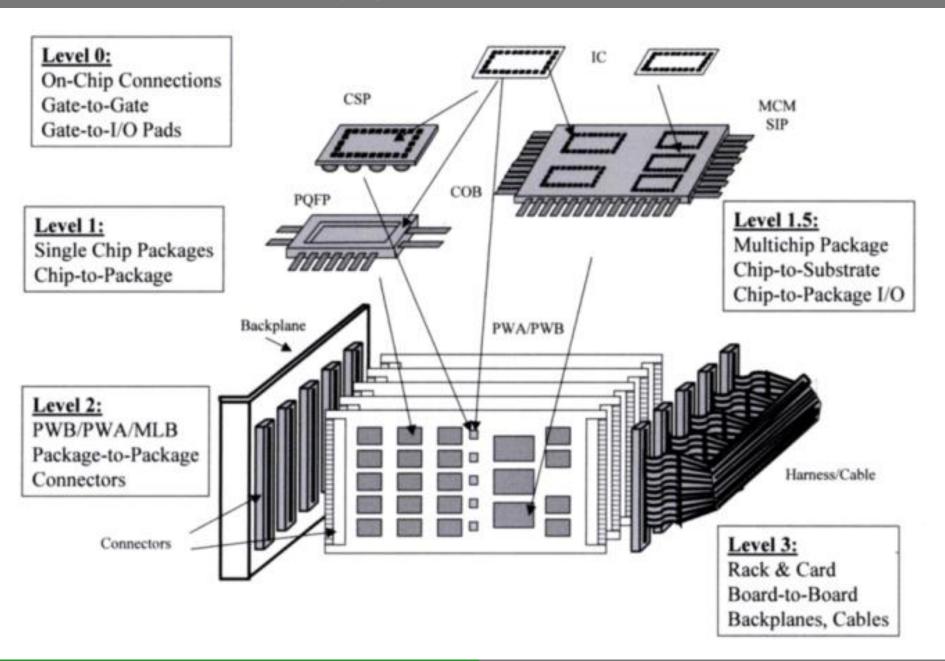

# Type of electronic packaging levels

- The first-level packaging consists of the interconnection and encapsulation of the IC chip.

- The second-level packaging consists of the connection of the microelectronic package to the PCB.

- PCBs may be further interconnected to a motherboard, known as third-level packaging.

- The fourth and final packaging level is the packaging of the motherboard (or PCBs) in an electronic system such as a laptop computer or a cellular phone.

# Chip configuration / arrangement

- Single chip (SCP)

- Single chip package is a package that supports a single microelectronic device so that its electrical, mechanical, thermal, and chemical performance needs are adequately served

## System on chip (SOC)

It is an integrated circuit that integrates all or most components of a computer or other electronic system (CPU, memory, input/output ports and secondary storage) on a single substrate or microchip.

SOC complete system on one chip

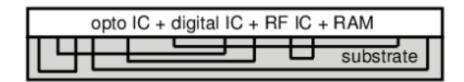

# Multi chip module (MCM)

- An electronic assembly where multiple integrated circuits (ICs or "chips"), semiconductor dies and/or other discrete components are integrated, usually onto a unifying substrate.

- Other terms for MCM packaging include "Heterogeneous integration" or "Hybrid Integrated Circuit"

MCM interconnects components

- System in package (SIP)

- It is a number of integrated circuits enclosed in one or more chip carrier packages that may be stacked using package on package.

- The SIP performs all or most of the functions of an electronic system, and is typically used inside a mobile phone, digital music player, etc.

- Dies containing integrated circuits may be stacked vertically on a substrate. They

are internally connected by fine wires that are bonded to the package

SIP-IC

RAM

analog

digital

SIP-PACKAGE

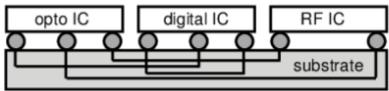

- System on package (SOP)

- It is an emerging system technology that goes beyond System-on-Chip (SOC) and System-in-Package (SIP) and forms the basis of all emerging digital convergent electronic and bioelectric systems.

- Therefore, overcomes both the computing and integration limitations of SOC, SIP,

MCM and traditional system packaging.

- Stacked chip

- Package interposer package (PiP)/ Package on package (PoP)

- 3D Packaging

# Further, it can be classified as

- **Standard** This is the most common packaging. The pins are spaced 0.1" apart.

- DIP (Dual In-line Package)

- DIPH (DIP with heat sink)

- SIP (Single In-line Package)

- SIPH (SIP with heat sink)

- ZIP (Zigzag In-line Package)

- ZIPH (ZIP with heat sink)

- PGA (Pin Grid Array)

- **Skinny** In this packaging, the space between the terminal rows is 7.62mm.

- SKDIP (Skinny DIP)

- **Shrink** Similar to the standard ones but the lead pitch is 1.778 mm. Smaller in size, they use high pin density packaging.

- SDIP (Shrink DIP)

- SDIPH (Shrink DIP with heat sink)

- SSIP (Shrink SIP)

- SZIP (Shrink ZIP)

# Budapest University of Technology and Economic Department of Electron Devices

# **Circuit Environment**

# Lecture 5

**Modern Packaging Solutions**

By: SALAM AL-ABASSI

#### **Reviews**

- The raw material for silicon manufacture is sand.

- The sand is heated in a furnace containing a source of carbon.

$$2C + SiO2 \longrightarrow (MGS) Si (98\%) + 2CO$$

Raw Material and Purification(EGS)

Si (s) + 3HCl (g)

$$\longrightarrow$$

SiHCl3 (g) + H2 (g) + heat

■ To convert the SiHCl3 back into purified Si a CVD (Chemical Vapor Deposition) process is used (in a hydrogen atmosphere).

- MONOCRYSTAL SILICON GROWTH

- Finally, Silicon Wafer is ready

# Example

# Packaging Technology Evolution

# **Packaging Technology Evolution**

Increasing

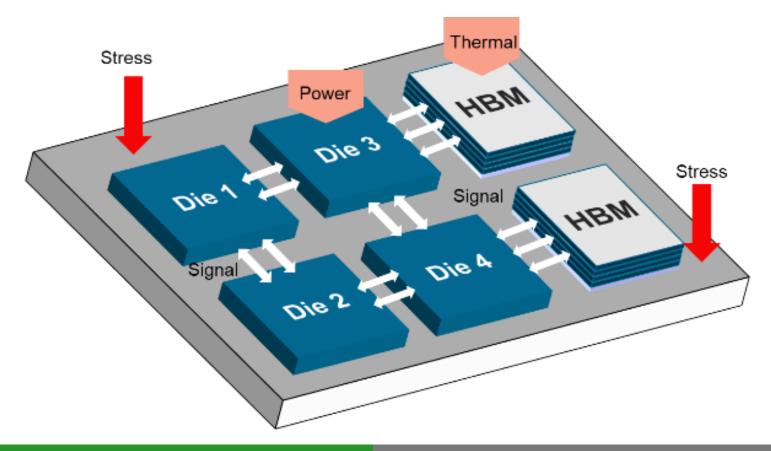

# Challenges of IC packaging

- Identifying and accommodating the electrical, mechanical and thermal requirements inherent in the IC,

- Selecting those manufacturing technologies that incorporate attributes that will contribute to an end product that is "smaller, better, and cheaper".

## **Functions of Semiconductor Packaging**

Typical electronic product.

It consists of printed circuit boards (PCBs) with some semiconductor integrated circuit (IC) chip components.

IC chip is not an isolated island.

It must communicate with other

IC chips in a circuit through

an input/output (I/O) system of interconnects.

One of the packaging functions is to distribute the signals onto and off the IC Cross-section chip. Molding Compound Au/Cu wire Solder Bump Underfil IC Chip A IC Chip B Lead-frame Package Solder Substrate Joint Solder Joint Cu Trace Printed Circuit Board

# Why Packaging?

- The IC chip and its embedded circuitry are sensitive, requiring the package to both carry and protect it.

- the major functions of the semiconductor packaging are, for example :

- (1) to provide a path for the electrical current that powers the circuits on the IC chip;

- (2) to distribute the signals onto and off the IC chip;

- (3) to remove the heat generated by the circuits on the IC chip;

- (4) to support and protect the IC chip from hostile environments.

# **Level of Semiconductor Packaging**

# Different semiconductor packaging

# Leadframe

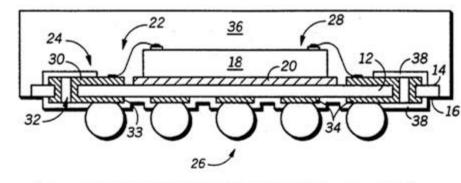

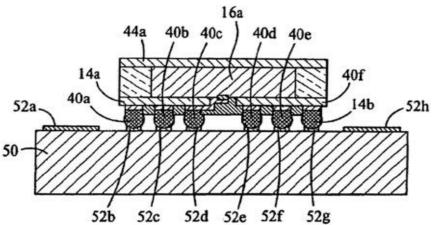

- July 17, 1967, by Kauffman.

- 14,16 are leadframes

- 18 is terminal ends of leadframes

- 20 is a chip

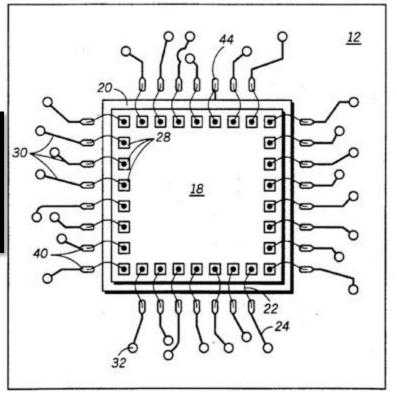

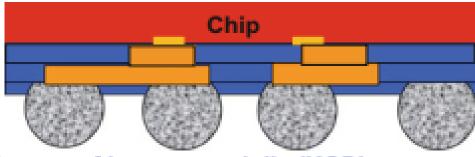

## **Organic Substrate with Solder Balls**

- March 2, 1992, by Paul Lin, Mike McShane, and Howard Wilson

- 12 is a substrate (organic carrier).

- 26 is solder balls (area array).

- 18 is a chip

- 22 is wire bond

- 32 is used to connect the top layer with bottom layer

The over molded pad array carrier (OMPAC) package which is the first PBGA

### The advantages of PBGA over leadframe are:

- (1) less package area for the same package pin count and thus less PCB real estate,

- (2) higher pin counts,

- (3) lower profile,

- (4) better in handling (no-bend leads),

- (5) better coplanarity,

- (6) better assembly yield because the forgiving of self-aligning characteristic of the surface tension of molten solder ball during reflow,

- (7) better in rework,

- (8) smaller inductance because of the short runs between the chip and the solder balls on the bottom of the substrate,

- (9) smaller reflections and noise levels, respectively, by matching the trace length with the output impedance,

- (10) better heat dissipation with copper power and ground planes

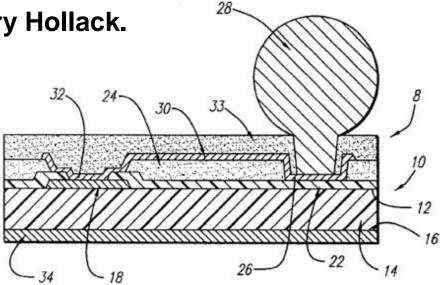

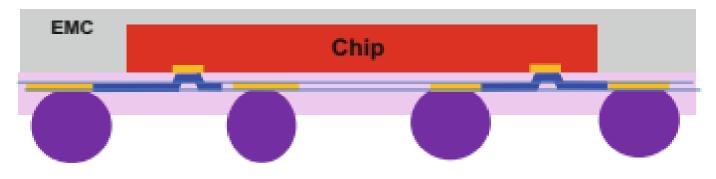

# Fan-In Wafer-Level Packaging

July 13, 1998, Peter Elenius and Harry Hollack.

- 30 is redistribution layer (RDL).

- 18,20 are bond pads.

- 10 is a chip.

- 14 is a wafer

- 28 is solder balls

- 32 is the electrical contact

- Leadframe, substrate and underfill are eliminated

- The packages made by the fan-in WLP are called wafer-level chip scale package (WLCSP)

## The advantages of WLCSPs over PBGA packages are

- (1) lower cost,

- (2) Lover profile,

- (3) small form factor,

- (4) simpler structure,

- (5) lighter,

- (6) less assembly steps,

- (7) better electrical performance,

- (8) eliminate the substrate, underfill, and one level of wafer bumping.

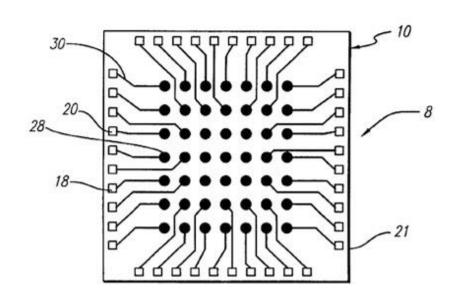

## **Fan-Out Wafer-Level Packaging**

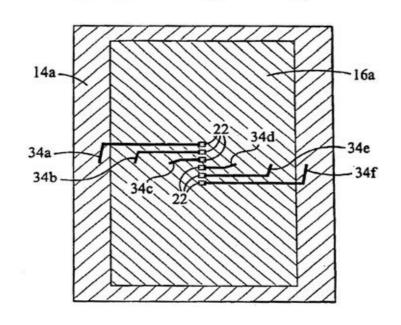

October 31, 2001, by Harry Hedler, Thorsten Meyer, and Barbara Vasquez

34a-f are RDLs.22s are metal pads.16a is a chip40a-f are solder balls52b-g are metal pads.14a-b are dielectric layers.

## Advantages of fan-out WLP over fcPBGA

- (1) lower cost

- (2) lower profile

- (3) eliminating the substrate

- (4) eliminating the wafer bumping

- (5) eliminating the flip chip reflow

- (6) eliminating the flux cleaning

- (7) eliminating the underfill

- (8) better electrical performance

- (9) better thermal performance

- (10) easier to go for system-in-package (SiP) and 3D IC packaging

# Advantages of fan-out WLP over fan-in WLP

- (1) the use of known good die (KGD)

- (2) better wafer-level yield

- (3) using the best of silicon

- (4) multichip

- (5) embedded integrated passive devices

- (6) more than one RDL

- (7) higher pin counts (or die shrink)

- (8) better thermal performance

- (9) easier to go for SiP and 3D IC packaging

- (10) higher PCB level reliability.

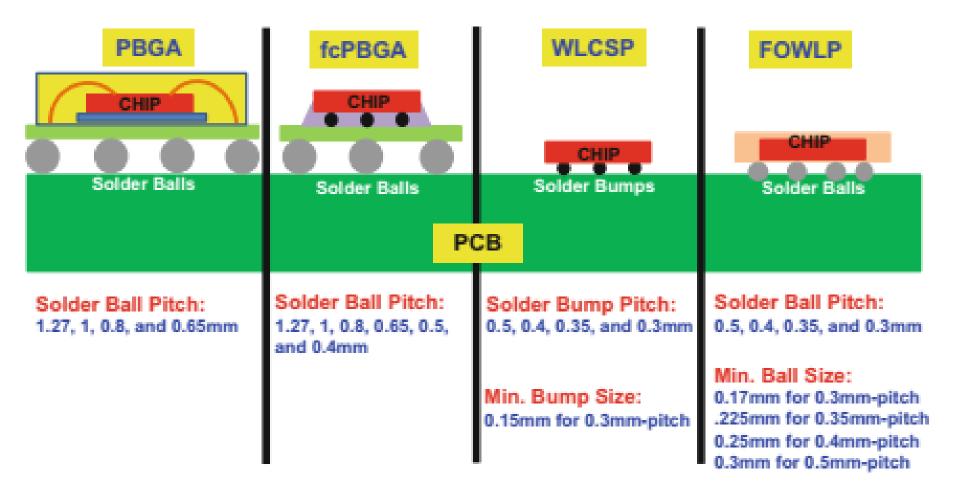

## Ball/Bump Pitch/Size of PBGA, fcPBGA, WLCSP, and FOWLP

#### References

- Fan-Out Wafer-Level Packaging (John H. Lau)

- Integrated Circuit Packaging, Assembly and Interconnections (William J. Greig )

# Budapest University of Technology and Economic Department of Electron Devices

## **Circuit Environment**

### Lecture 6

Parasitic effects of packaging

By: SALAM AL-ABASSI

# **Packaging Parasitic**

- The effects of packaging on RFICs.

- The effects of packaging on thermal management of ICs

Radio frequency integrated circuits (RFIC): are the devices that work at range of frequencies from 20kHz to 300GHz.

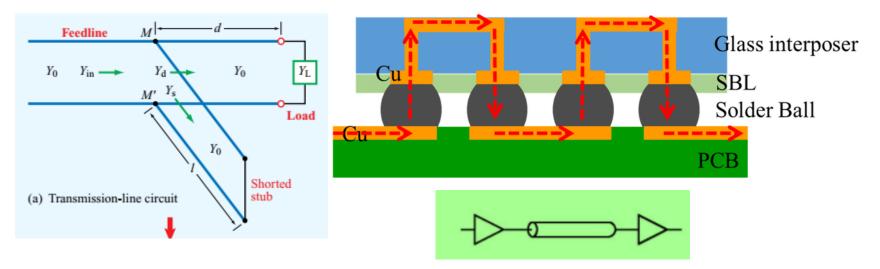

- in order to design radio frequency (RF) communications integrated circuits (IC) in the gigahertz range, it must deal with:

- 1- Transmission lines at chip interfaces.

- 2- Impedance matching is addressed.

$$u_{\rm p} = f\lambda$$

(m/s).

▶ When  $l/\lambda$  is very small, transmission-line effects may be ignored, but when  $l/\lambda \gtrsim 0.01$ , it may be necessary to account not only for the phase shift due to the time delay, but also for the presence of *reflected* signals that may have been bounced back by the load toward the generator. ◀

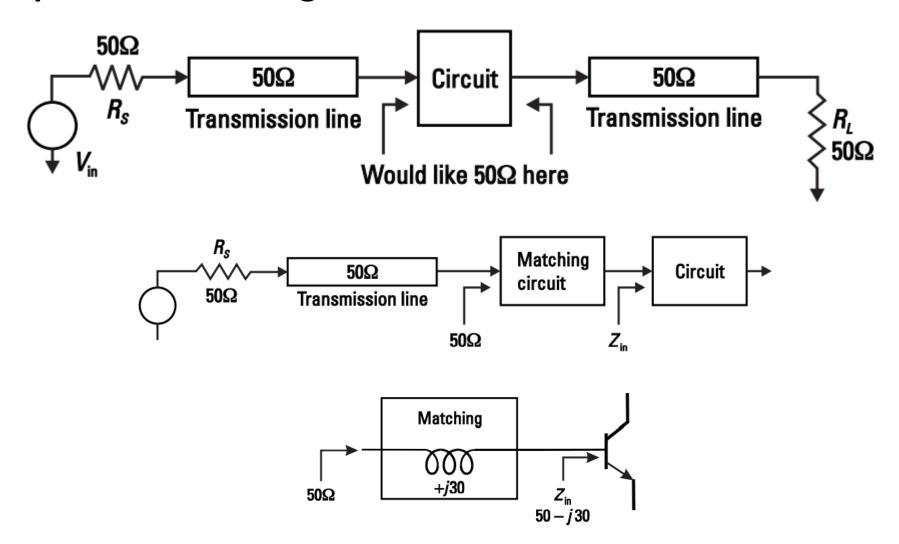

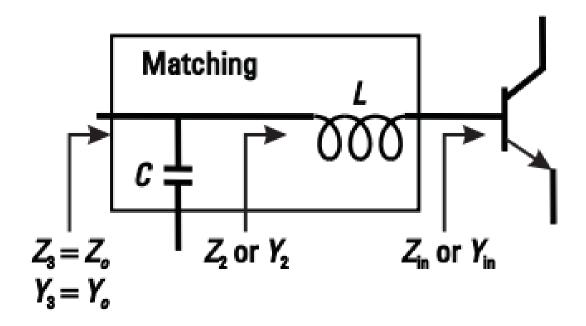

# Impedance matching

#### **Example:**

Use the matching network to match the transistor input impedance Zin =  $40 - j30 \Omega$  to Zo =  $50\Omega$ . Perform the matching at 2 GHz.

# Bringing it all Together:

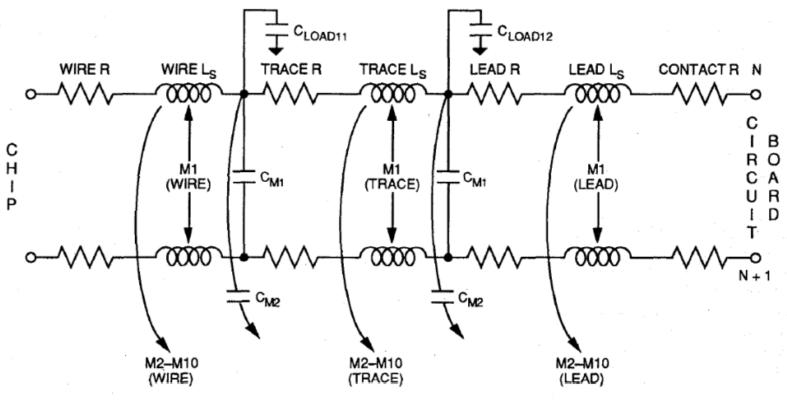

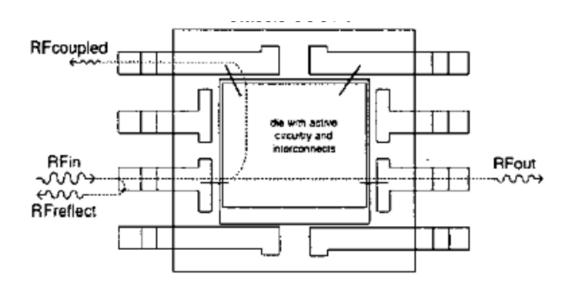

When combining the packaged IC and the PCB, there are several parasitic factors the IC designer and the PCB designer must consider for a high-performance circuit.

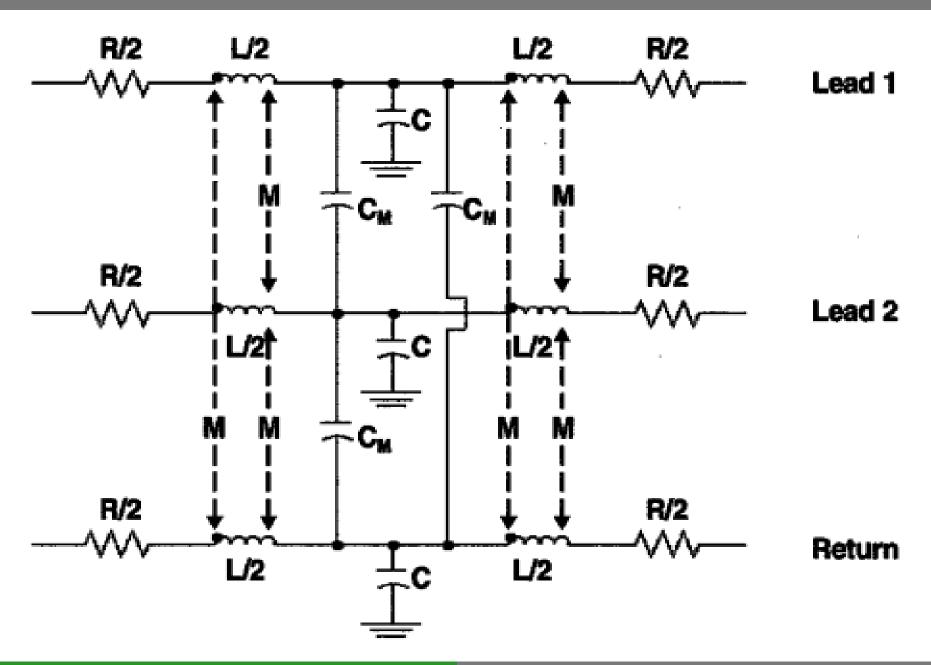

# Quad flat pack Equivalent electrical circuits

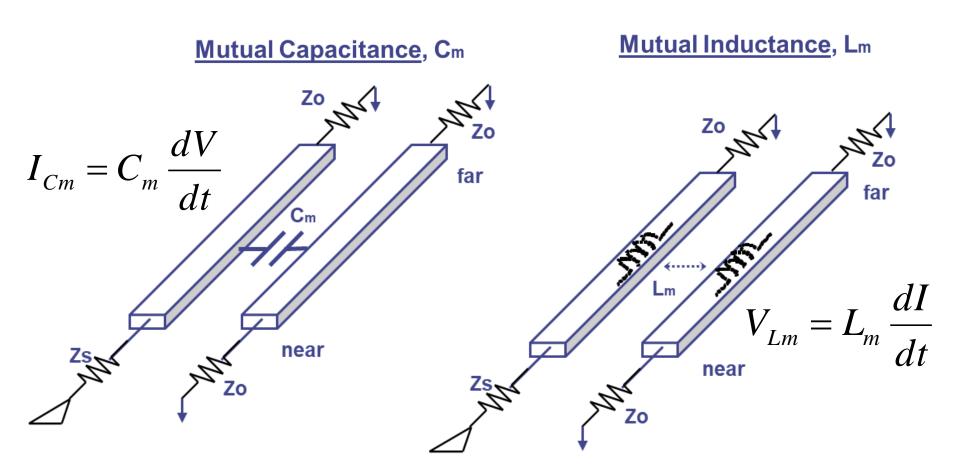

Note that there are a number of interacting mutual inductances (M), mutual capacitances (CM), as well as self inductances (Ls), self capacitances(C) and resistances (R).

Parasitic Elements

(self inductance, L; mutual inductance, Lm; self capacitance, C; mutual capacitance, Cm; input output pad capacitance, Cio; and resistance, R)

- Self inductance: is the inductance of the wire itself.

- Mutual inductance: is the inductance between adjacent wires.

- Self capacitance: is the capacitance between the wire and ground plane.

- Mutual capacitance: is the capacitance between two wires.

- Cio: is the capacitance created by the IO pads of the die and its carrier where the bond wires are connected.

- Resistance: is simply the resistance of the wire which is affected by the skin depth of the wire.

- Skin depth: is the depth that current is carried in wires which becomes shallower as frequency increases.

#### **Sheet Resistance**

Sheet resistance: (also known as surface resistance or surface resistivity)

is a common electrical property used to characterize thin

films of conducting and semiconducting materials.

$$\rho = \frac{1}{\sigma} \qquad \qquad R = \frac{\rho L}{Wt} \qquad \qquad \rho_s = \frac{\rho}{t} = R\left(\frac{W}{L}\right)$$

$$\text{corner} = 0.56 \text{ squares}$$

#### The Skin Effect

- Skin effect is usually described as the tendency of current to flow on the surface (skin) of a conductor as frequency increases.

- Because the inner regions of the conductor are less effective at carrying current than at low frequencies.

- The useful cross-sectional area of a conductor is reduced, thereby producing a corresponding increase in resistance.

$$\delta = \sqrt{\frac{\rho}{\pi f \mu}}$$

Skin depth of some common metals over the frequency band of interest.

Skin Depth of Various Metals at Various Frequencies

| Metal    | $ ho(\mu\Omega\cdot{ m cm})$ | 500 MHz              | 1 GHz                | 2 GHz                | 5 GHz                 | 10 GHz                |

|----------|------------------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|

| Gold     | 2.44                         | $3.5~\mu\mathrm{m}$  | 2.5 $\mu$ m          | 1.8 $\mu$ m          | 1.1 $\mu$ m           | 0.79 μm               |

| Tungston | 5.49                         | $5.3 \mu \text{m}$   | $3.7~\mu$ m          | $2.6~\mu \mathrm{m}$ | $1.7~\mu$ m           | $1.2 \mu \text{m}$    |

| Aluminum | 2.62                         | $3.6~\mu \mathrm{m}$ | $2.6~\mu \mathrm{m}$ | $1.8~\mu \mathrm{m}$ | 1.2 μm                | $0.82~\mu\mathrm{m}$  |

| Copper   | 1.72                         | $3.0 \mu$ m          | $2.1 \mu \mathrm{m}$ | $1.5 \mu \mathrm{m}$ | $0.93 \mu \mathrm{m}$ | $0.66 \mu \mathrm{m}$ |

| Silver   | 1.62                         | $2.9~\mu\mathrm{m}$  | $2.0~\mu\mathrm{m}$  | $1.4~\mu\mathrm{m}$  | $0.91~\mu\mathrm{m}$  | $0.64~\mu\mathrm{m}$  |

| Nickel   | 6.90                         | $5.9~\mu$ m          | 4.2 $\mu$ m          | $3.0~\mu\mathrm{m}$  | 1.9 $\mu$ m           | 1.3 $\mu$ m           |

# Example:

• A rectangular aluminum line has a width of 20 μm, a thickness of 3 μm, and a length of 100 μm. Compute the resistance of the line at dc and at 5 GHz assuming that all the current flows in an area one skin depth from the surface. Assume that aluminum has a resistivity of 3 μΩ.cm.

Ans:

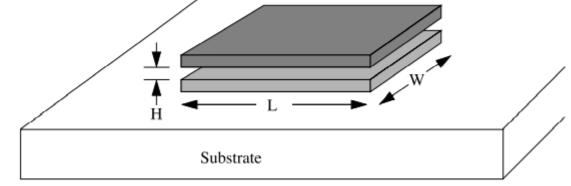

#### **Parasitic Capacitance**

All of the interconnect layers may be used to make traditional parallel plate capacitors

$$C \approx \varepsilon \frac{A}{H} = \varepsilon \frac{W \cdot L}{H},$$

Dielectric layer tends to be rather thick (order of 0.5–1 μm),

precisely to reduce the capacitance between layers

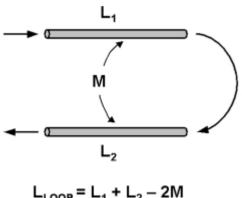

#### **Parasitic Inductance**

- Inductance (L) is defined as the relationship between the following for a closed current path:

- flux linkage (Φ) and current flow (i): Φ = L × i

- time varying voltage (v) and current (i): v = L × di /dt

- On an IC package, signals propagate in and out through the signal leads and return through the power leads.

- The closed current path (or loop) is formed by signal leads together with power or ground leads.

#### **Parasitic Inductance**

- Due to the non idealities (i.e.parasitic R, L, C) of packages.

- The RF input signal is reflected, transmitted and coupled throughout the die.

- Performance of ICs will be degradation in the form of:

- -insufficient Return Loss(RL)

- -excessive Insertion Loss(IL)

- -reduced pin to pin isolation

- -reduction of bandwidth

- -linearity.

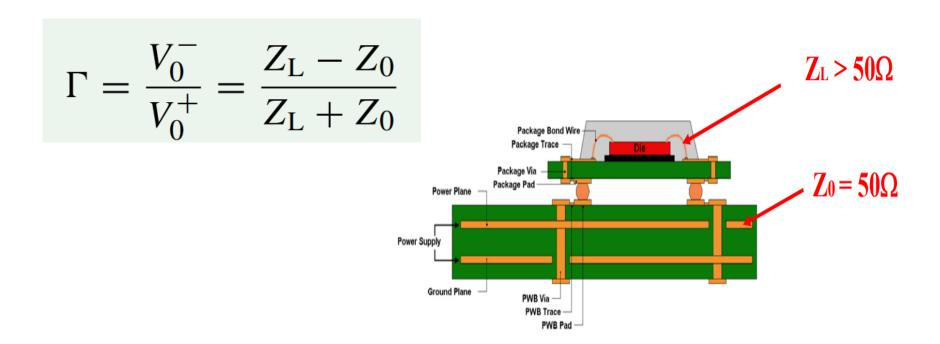

## Why is packaging limiting performance?

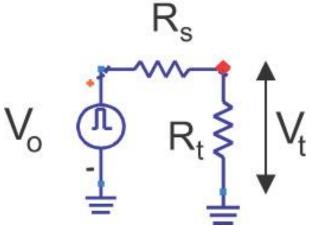

- Inductive Interconnect Leads to Reflections

- Interconnect is not matched to system.

- Reflections occur due to interconnect.

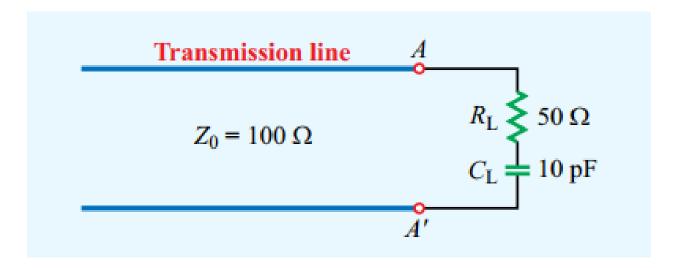

#### **Example:**

A  $100\Omega$  transmission line is connected to a load consisting of a  $50\Omega$  resistor in series with a 10pF capacitor. Find the reflection coefficient at the load for a 100 MHz signal.

#### **Current Solution to Reflections**

- Live with the Signal Path Reflections.

- 1) Run the signals slow enough so that reflections are small.

- \* Limits System Performance

$$\Gamma = \frac{Z_L - Z_0}{Z_L + Z_0} < 10\%$$

2) Terminate Signals on the Mother board so that reflections are absorbed.

\*This only eliminates primary reflections, the second still exists

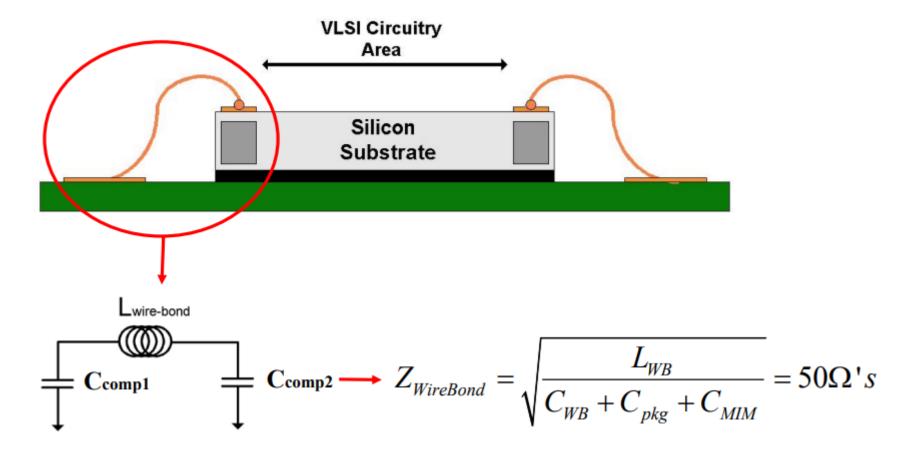

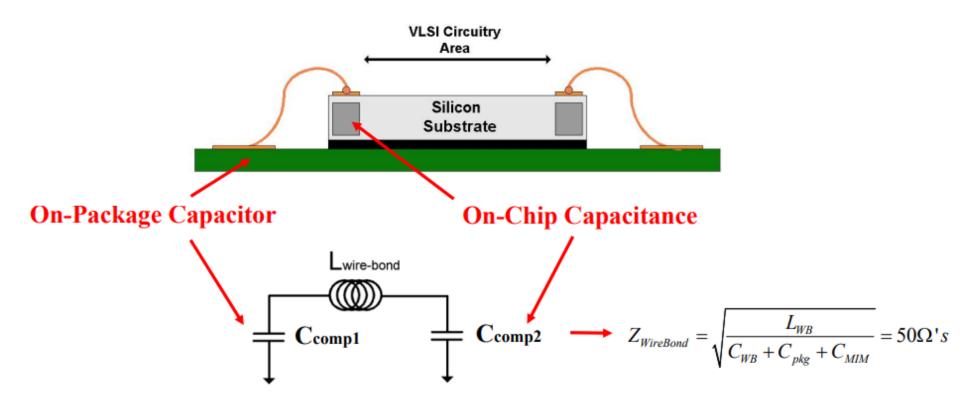

# Add Capacitance Near Bond Wire to Reduce Impedance

- Adding additional capacitance lowers the wire bond impedance

- Impedance can be matched to system, reducing reflections

$$Z_{WireBond} = \sqrt{\frac{L_{WireBond}}{C_{WireBond}}} - \text{Add Capacitance to lower Z}$$

Capacitance on the IC or Package is close enough to alter impedance

# Capacitor values chosen prior to fabrication

Equal amounts of capacitance are used on-chip and on-package.

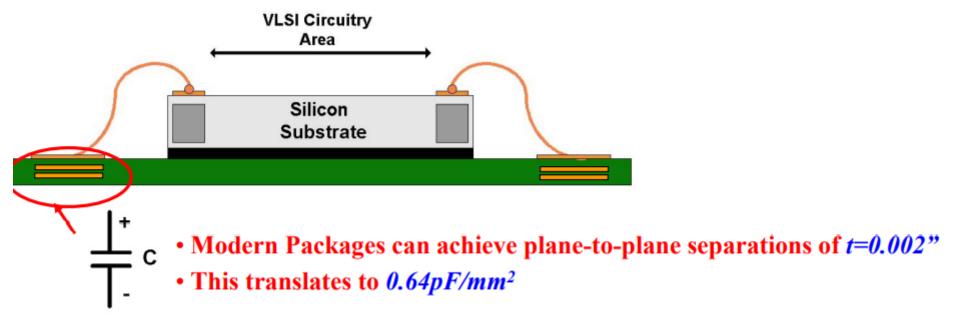

# **On-Package Capacitors**

- Embedded capacitor construction is used

- No components are needed, reducing package cost

- Capacitance values needed can be implemented using this construction

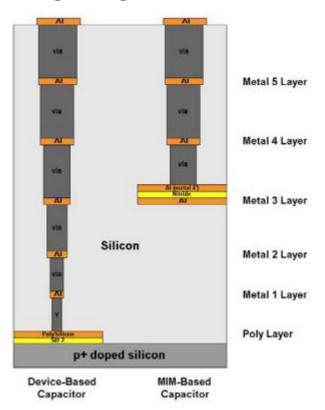

# **On-Chip Capacitor**

- Device and MIM capacitors are evaluated

- Targeting area beneath wire bond pad, which is typically unused.

#### 0.1um BPTM Process

• Device-Based Capacitor : 13 fF/um<sup>2</sup>

• MIM-Based Capacitor : 1.1 fF/um<sup>2</sup>

# Wire Bond Modeling

- Typical VLSI wire bond lengths range from 1mm to 5mm

- Electrical parameter extraction is used to find L and C or wire bond

| <b>Length</b> | $\underline{\mathbf{L}}$ | <u>C</u>    | $\mathbf{Z}_0$ |

|---------------|--------------------------|-------------|----------------|

| 1mm           | 0.569nH                  | <b>26fF</b> | 148Ω           |

| 2mm           | 1.138nH                  | <b>52fF</b> | 148Ω           |

| 3mm           | 1.707nH                  | <b>78fF</b> | 148Ω           |

| 4mm           | 2.276nH                  | 104fF       | $148\Omega$    |

| 5mm           | 2.845nH                  | 130fF       | $148\Omega$    |

#### References

Radio Frequency Integrated Circuit Design John (Rogers, Calvin Plett)

# Budapest University of Technology and Economic Department of Electron Devices

## **Circuit Environment**

Lecture 8

**Signal Integrity**

By: SALAM AL-ABASSI

Sal-abassi@edu.bme.hu

There are two kinds of engineers:

Those who have signal-integrity

problems and those who will. Eric Bogatin

Signal Integrity (SI) is the ability of a system to transfer (data) signals without excessive distortion.

• SI is an important concern in High-Speed Digital Design

- All engineers who touch a product should have an understanding of how what they do may influence the performance of the overall product.

- By understanding the essential principles of signal integrity at an intuitive and engineering level,

- Every engineer involved in the design process can evaluate the impact of his/her decisions on system performance.

- This lecture is about the essential principles needed to understand signal integrity problems and their solutions.

- The engineering discipline required to deal with these problems is presented at **an intuitive level and a quantitative level**.

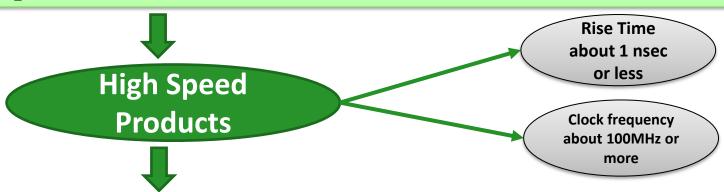

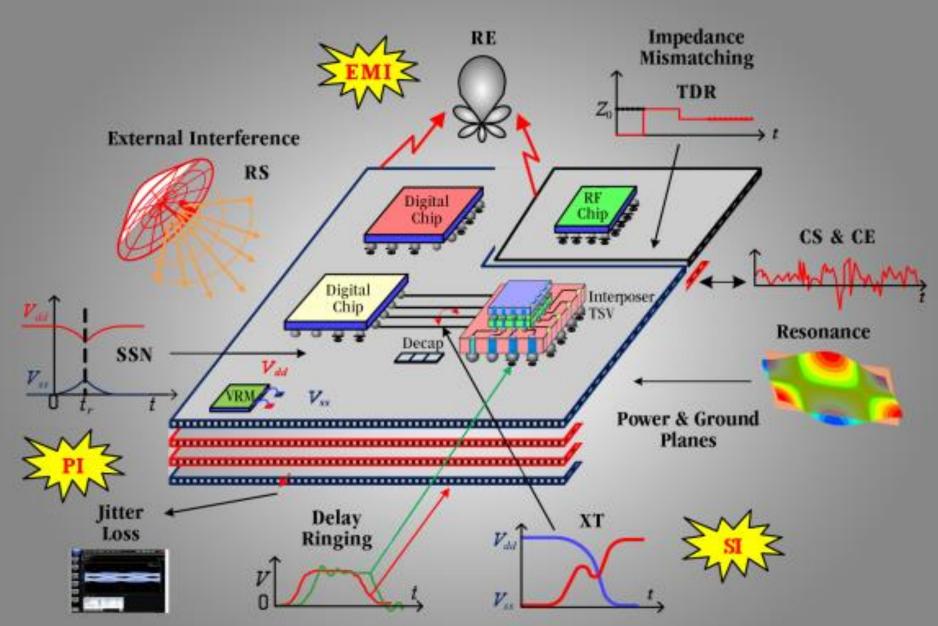

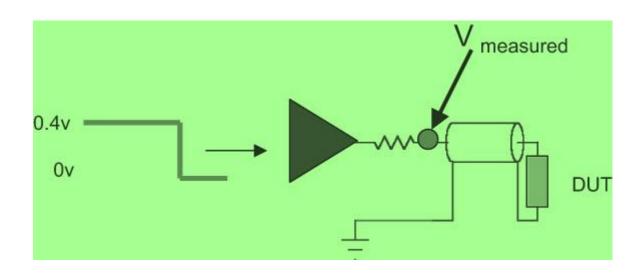

## What are SI, PI and EMC

For most electronic products, signal-integrity effects begin to be important at clock frequencies above about 100 MHz or rise times shorter than about 1 nsec.

how the electrical properties of the interconnects, interacting with the digital signal's voltage and current waveforms, can affect performance.

- 1. Signal integrity (SI), involving the distortion of signals.

- 2. Power integrity (PI), involving the noise on the interconnects and any associated components delivering power to the active devices.

- **3. Electromagnetic compatibility (EMC)**, the contribution to radiated emissions or susceptibility to electromagnetic interference from fields external to the product

In the design process, all three of these electrical performance issues need to be considered for a successful product.

Modeling and Design of Electromagnetic Compatibility for High-Speed Printed Circuit Boards and Packaging (Xing-Chang Wei)

# **Electromagnetic compatibility (EMC)**

- The general area of EMC really encompasses solutions to two problems:

- 1. Too much radiated emission from a product into the outside world

- 2. Too much interference on a product from radiation coming from the outside world.

- EMC is about engineering solutions for the product so it will at the same time maintain radiated emissions below the acceptable limit and not be susceptible to radiation from the external world.

- Designing for acceptable EMC involves good SI and PI design as well as additional considerations, especially related to cables, connectors, and enclosure design.

- Spread spectrum clocking (SSC), which purposely adds jitter to clocks by modulating their clock frequency, is specifically used to pass an EMC certification test.

# **About jitter**

- Jitter: variations in the timing of the signal

- Signal is sampled at defined bit times

- Signal transitions must occur between sample times

- Can cause undefined or incorrect values at sample times

- Creates bit errors

- Many different types of jitter:

- Data dependent jitter

- Periodic jitter

- Random jitter

- etc.

# Power integrity (PI)

- PI is about the problems associated with the power distribution network (PDN), which includes all the interconnects **from the voltage regulator modules (VRMs)** to the voltage rail distributed on the die. This includes:

- 1. The power and ground planes in the board and in the packages,

- 2. The vias in the board to the packages,

- 3. The connections to the die pads,

- 4. Any passive components like capacitors connected to the PDN.

- Since the PDN that feeds the on-die core power rail, sometimes referred to as the *Vdd rail*, is exclusively a PI issue,

- So, there are many overlapping problems between PI and SI topics.

- This is primarily because the **return paths** for the signals use the same interconnects usually associated with the PDN interconnects, and anything that affects these structures has an impact on both **signal quality** and **power quality**.

#### Note:

The overlap between PI and SI problems adds confusion to the industry because problems in this gray area are either owned by two different engineers or fall through the cracks as the PI engineer and the SI engineer each think it's the other's responsibility.

# Signal integrity (SI)

- In the SI domain, problems generally relate to either:

- 1. Noise issues

- 2. Timing issues,

- Each of which can cause false triggering or bit errors at the receiver.

## Timing issues

- Timing is a complicated field of study. In one cycle of a clock, a certain number of operations must happen.

- This short amount of time must be divided up and allocated, in a budget, to all the various operations. For example, some time is allocated:

- 1. For gate switching,

- 2. For propagating the signal to the output gate,

- 3. For waiting for the clock to get to the next gate,

- 4. For waiting for the gate to read the data at the input.

- Though the interconnects affect the timing budget,

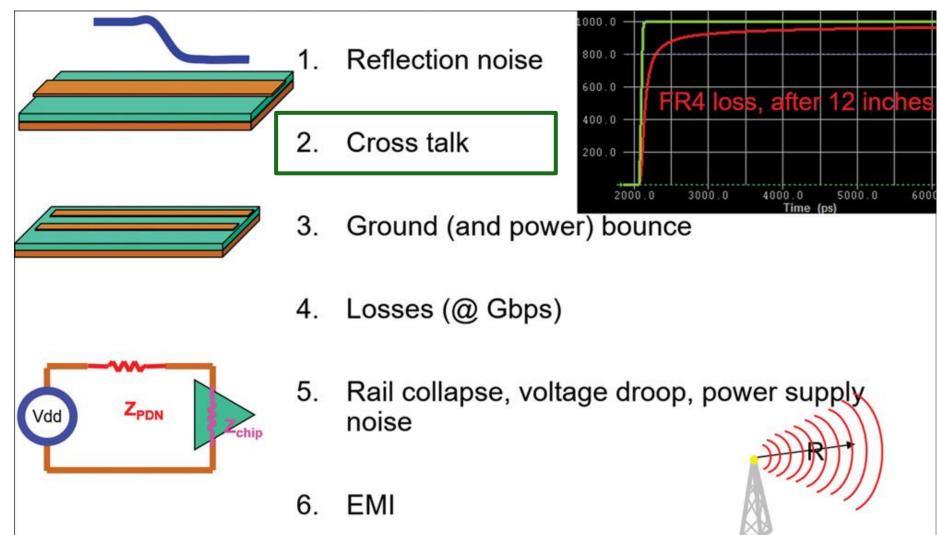

## Signal-Integrity noise problems

TERMINATIONS LINE DELAY

EMISSIONS

ATTENUATION POWER AND

NON-MONOTONIC EDGES

GROUND BOUNCE

GROUND DISTRIBUTION

SUSCEPTABILITY

SKIN DEPTH

SIGNAL INTEGRITY

LOSSY LINES IR DROP

INDUCTANCE

RINGING

RISE TIME DEGRADATION

PARASITICS

EMI/EMC

CROSSTALK

CAPACITANCE

LOADED LINES

STUB LENGTHS

CRITICAL NET

MODE CONVERSION

RETURN CURRENT PATH

GAPS IN PLANES

TRANSMISSION LINES

DELTA I NOISE

REFLECTIONS

UNDERSHOOT, OVERSHOOT

RC DELAY

IMPEDANCE DISCONTINUITIES

DISPERSION

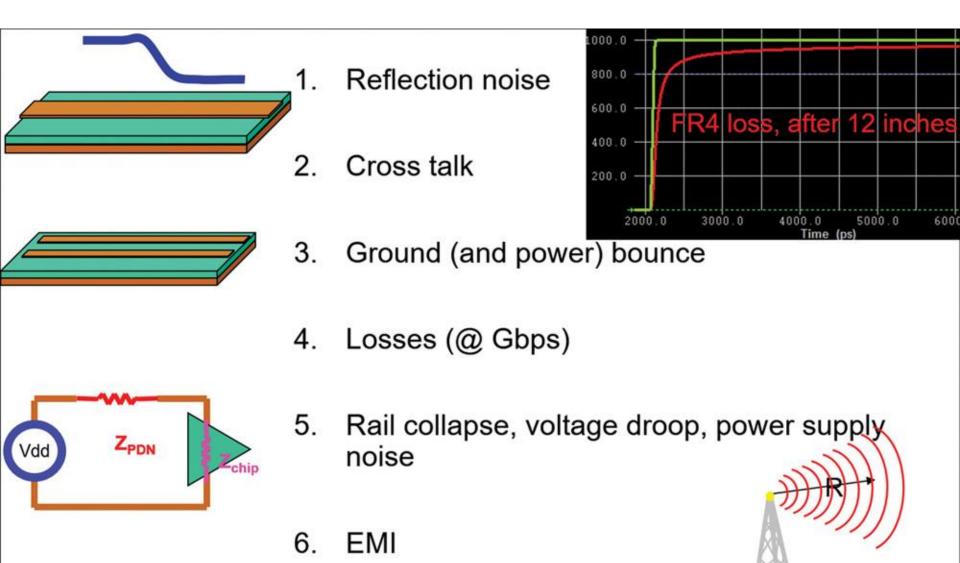

# Classify every SI/PI/EMC problem into one of these six families.

# **Keep in your Mind**

- These problems play a role in all interconnects, from the smallest on-chip wire to the cables connecting racks of boards and everywhere in-between.

- The essential principles and effects are the same.

- The only differences in each physical structure are the specific geometrical feature sizes and the material properties.

### SIGNAL-INTEGRITY EFFECTS ON ONE NET

- A net is made up of all the metal connected together in a system.

- There are three common problems associated with signals on a single net being distorted by the interconnect.

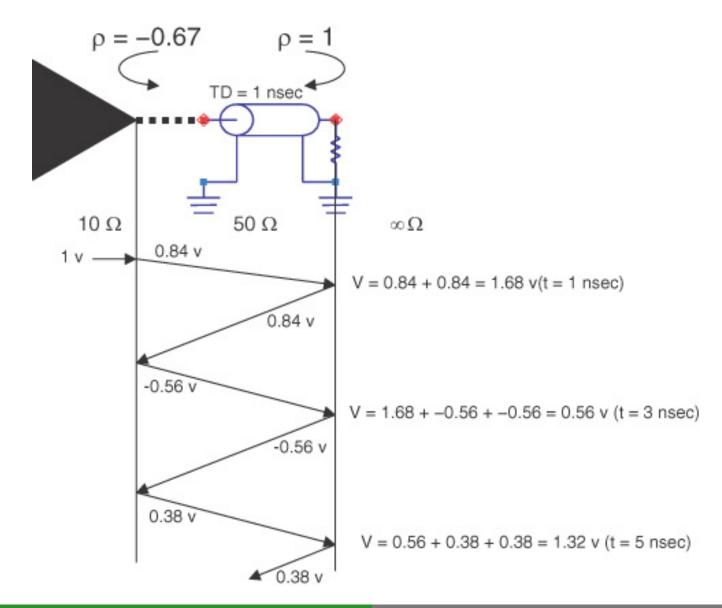

- 1. Reflections. [The only thing that causes a reflection is a change in the instantaneous impedance the signal encounters].

- 2. Frequency-dependent losses in the line from the conductor and the dielectric.

- 3. Timing. [The time delay difference between two or more signal paths is called skew. When a signal and clock line have a skew different than expected, false triggering and errors can result].

## SIGNAL-INTEGRITY EFFECTS ON ONE NET.

## Reflections

- The instantaneous impedance the signal sees depends as much on the physical features of the signal trace as on the return path.

- If there are enough impedance changes, the distortions can cause false triggering.

- Some of the features that would change the impedance the signal sees include the following:

- 1. An end of the interconnect

- 2. A line-width change

- 3. A layer change through a vias

- 4. A gap in return-path plane

- 5. A connector

- 6. A routing topology change, such as a branch, tee, or stub

## Reflections

The way to minimize the problems associated with impedance changes is to keep the instantaneous impedance the signal sees constant throughout the net.

- This strategy is typically implemented by following four best design practices:

- Use a board with constant, or "controlled," impedance traces. This usually 1. means using uniform transmission lines.

- To manage the reflections from the ends, use a termination strategy that 2. controls the reflections by using a resistor to fool the signal into not seeing an impedance change.

- Use routing rules that allow the topology to maintain a constant impedance 3. down the trace.

- Engineer the structures that are not uniform transmission lines to reduce their 4. discontinuity. This means adjusting fine geometrical design features to carve the fringe fields.

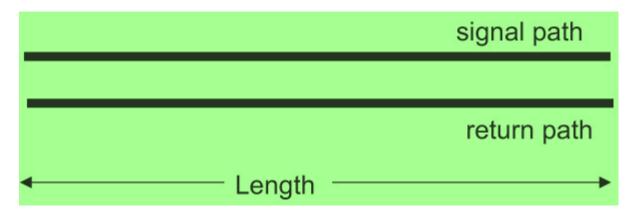

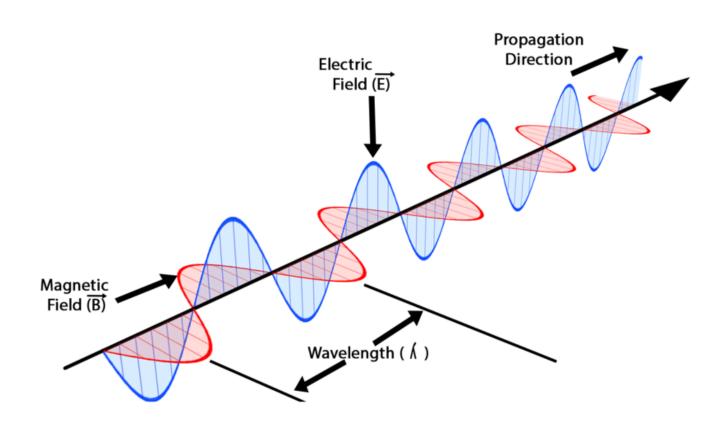

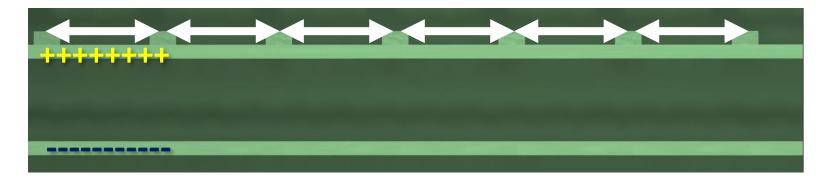

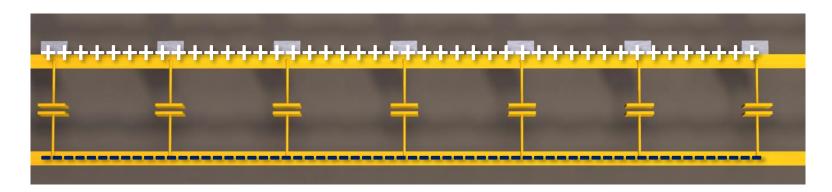

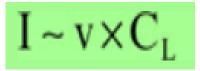

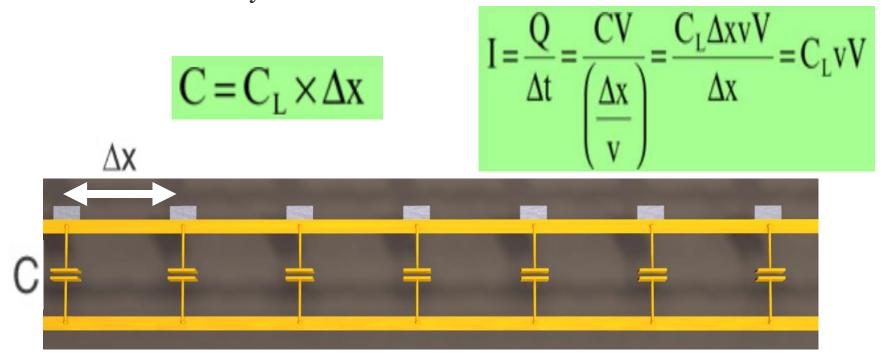

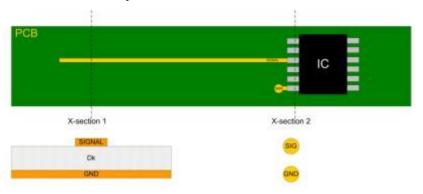

### The Physical Basis of Transmission Lines

- Transmission line is composed of any two conductors that have length.

- Transmission line is used to transport a signal from one point to another.

• **Transmission line** has two very important parameters: a characteristic impedance (ohm) and a time delay (second).

### FORGET THE WORD GROUND

- The term *ground* is reserved for the conductor with the lowest voltage in the circuit compared to any other node in the circuit.

- Using the term **ground** to refer to the **return path** is a very bad habit and should be avoided.

- It is much healthier to get into the habit of calling the other conductor the *return* path.

- Many of the problems related to **signal integrity** are due to poorly designed return paths.

When we label the other path as ground, we typically think it is a universal sink for current. Return current goes into this connection and comes out wherever there is another ground connection.

This is totally wrong.

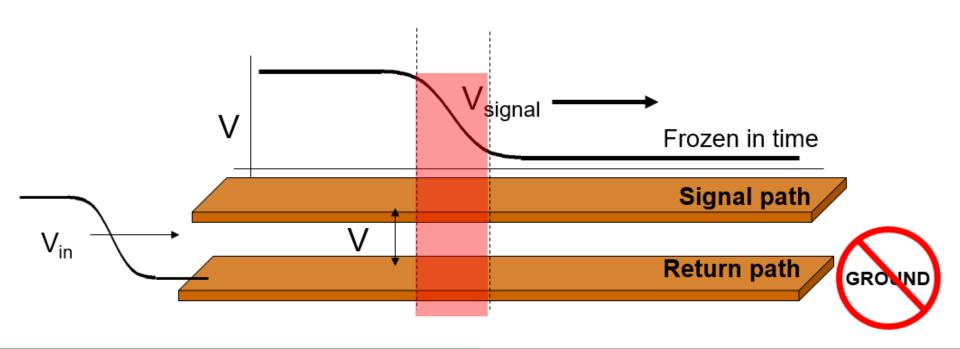

### THE SIGNAL

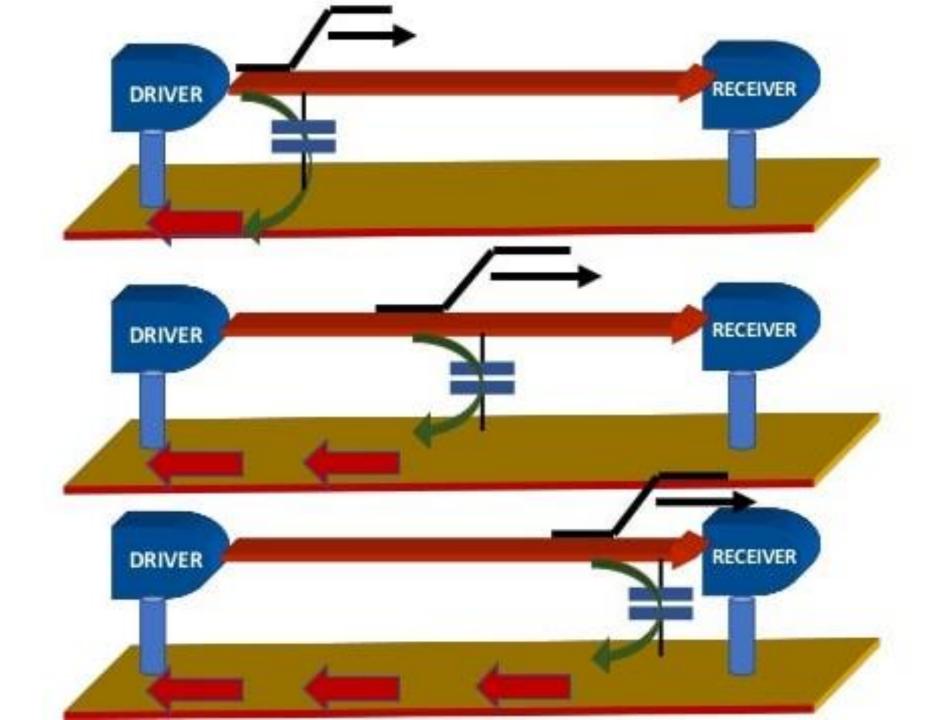

- When a signal moves down a transmission line, it simultaneously uses the signal path and the return path.

- **Both conductors** are equally important in determining how the signal interacts with the interconnect.

- When a signal is launched into a transmission line, it propagates down the line at the speed of light in the material.

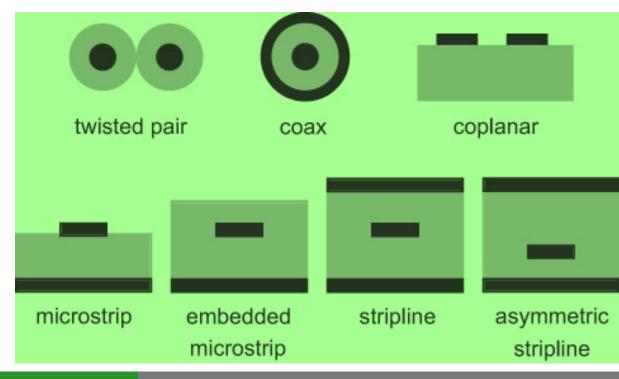

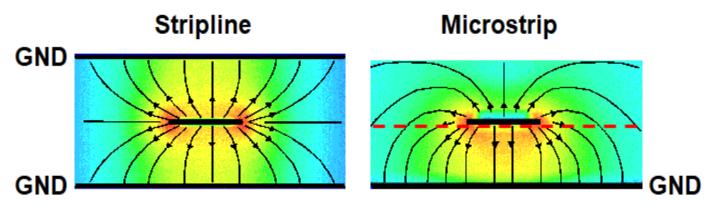

### UNIFORM TRANSMISSION LINES.

- Classify transmission lines by their geometry.

- The **uniformity** of the **cross section** down its length.=> uniform OR nonuniform.

Reflections will be minimized and signal quality optimized if the transmission lines are uniform or are controlled impedance. All high-speed interconnects should be designed as uniform transmission lines.

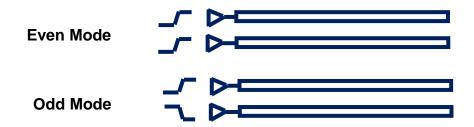

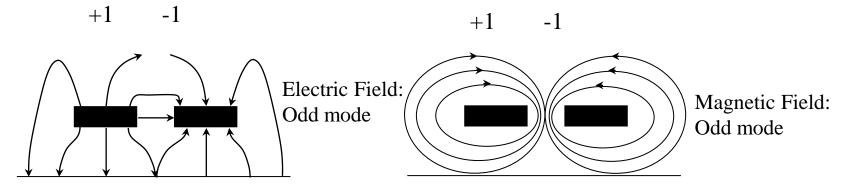

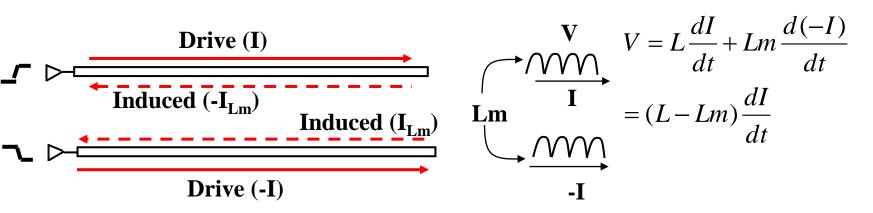

The identical of each of its two conductors.

## Keep in your Mind

In general, for most transmission lines, the signal quality and cross-talk effects will be completely unaffected by whether the line is balanced or unbalanced. However, ground-bounce and EMI issues will be strongly affected by the specific geometry of the return path.

Whether the transmission line is uniform or nonuniform, balanced or unbalanced, it has just one role to play: to transmit a signal from one end to the other with an acceptable level of distortion.

## How fast do signals travel down a transmission line?

- Is the speed of a signal the same THE SPEED OF ELECTRONS IN WIRE!!!()

- If reducing the resistance of the interconnect will increase the speed of a signal!!!

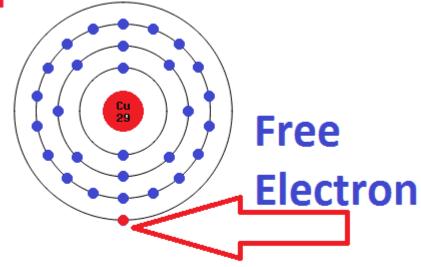

- In fact, the speed of the electrons in a typical copper wire is actually about 10 billion times slower than the speed of the signal.

## The speed of an electron in a copper wire?

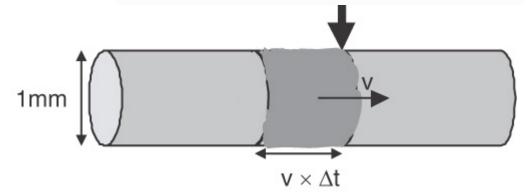

$$I = \frac{\Delta Q}{\Delta t} = \frac{q \times n \times A \times v \times \Delta t}{\Delta t} = q \times n \times A \times v$$

$$v = \frac{1}{q \times n \times A}$$

#### where:

I = current passing one point, in Amps

$\Delta Q$  = charge flowing in a time interval, in Coulombs

$\Delta t = time interval$

$q = charge of one electron = 1.6 \times 10^{-19} Coulombs$

n = density of free electrons, in #/m<sup>3</sup>

A = cross-sectional area of the wire, in m<sup>2</sup>

v = speed of the electrons in the wire, in m/sec

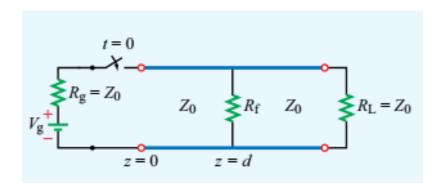

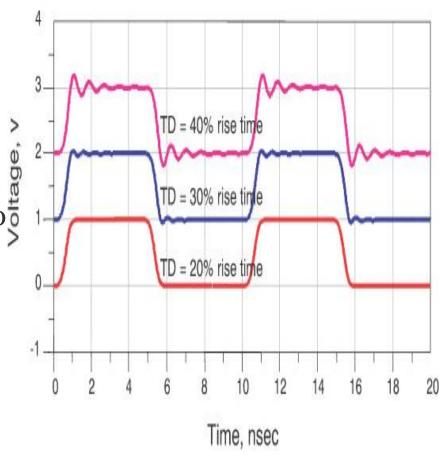

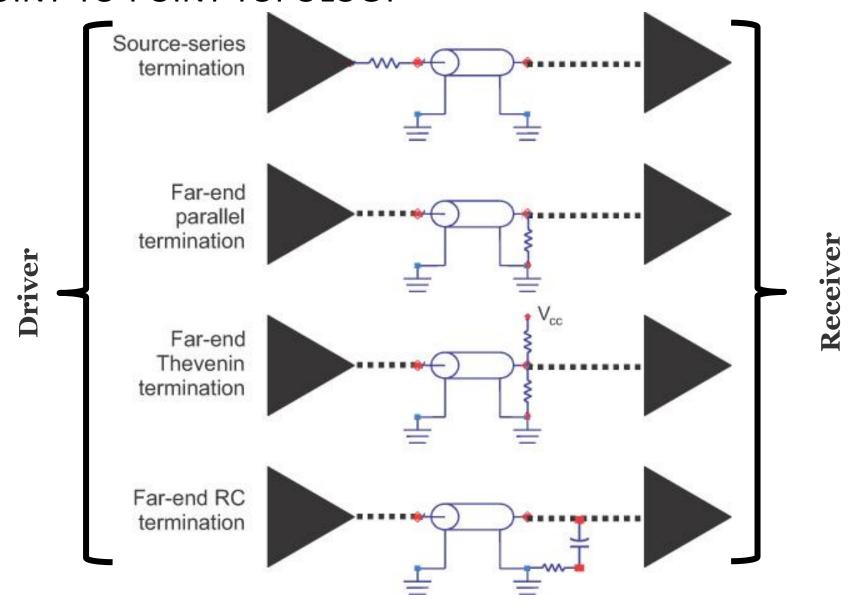

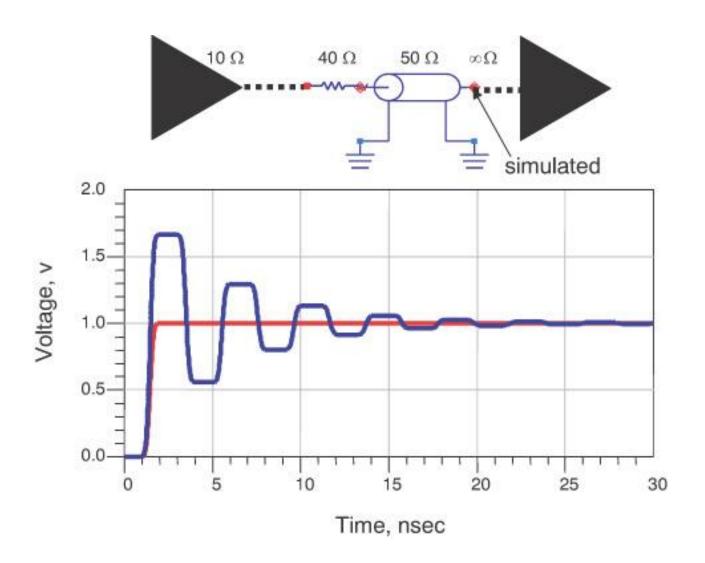

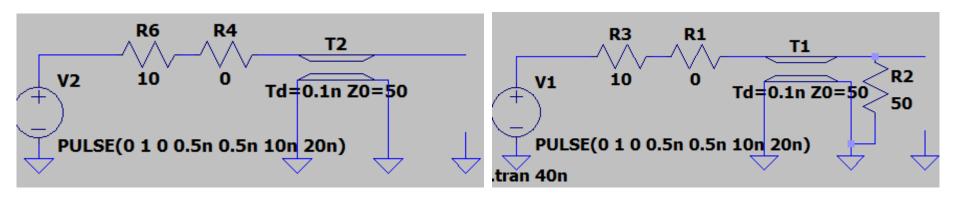

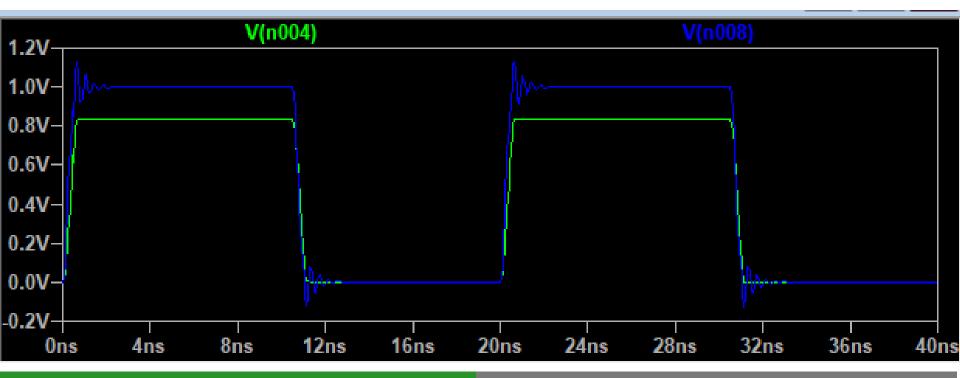

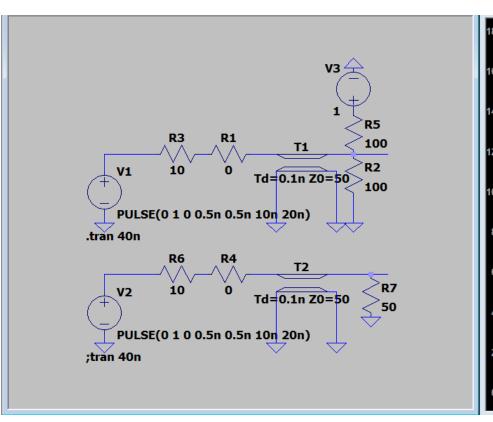

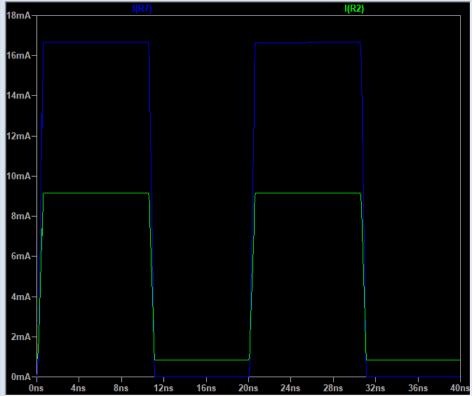

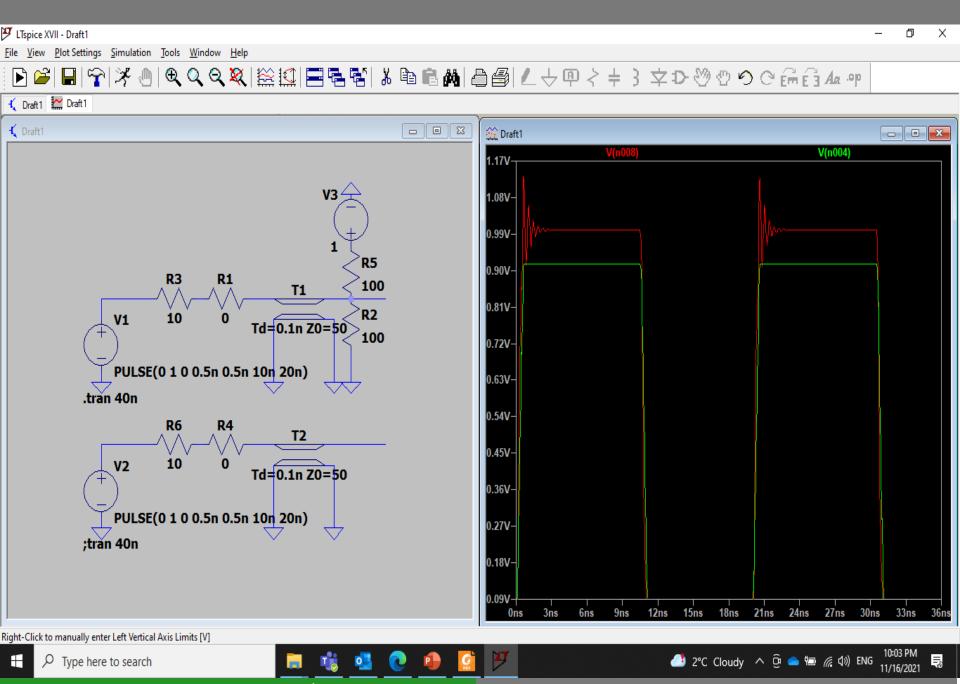

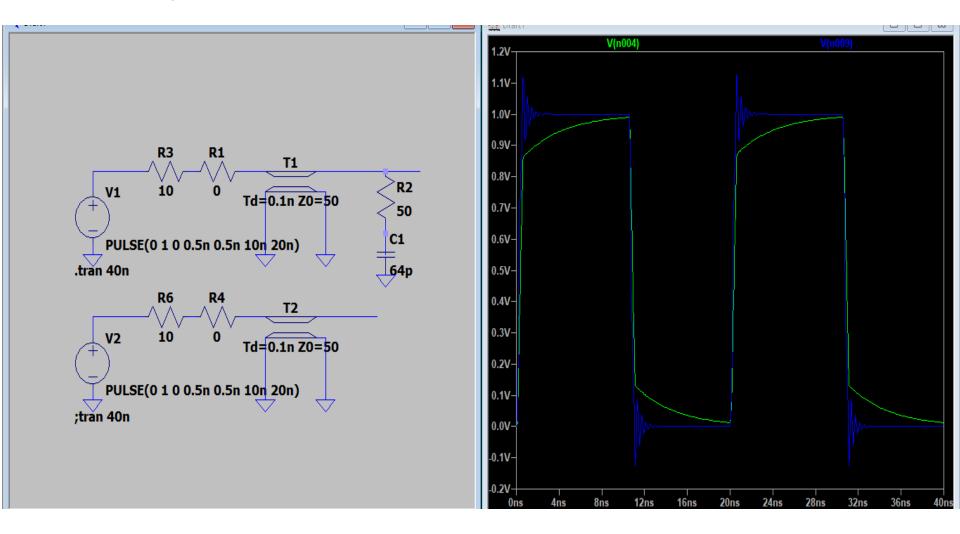

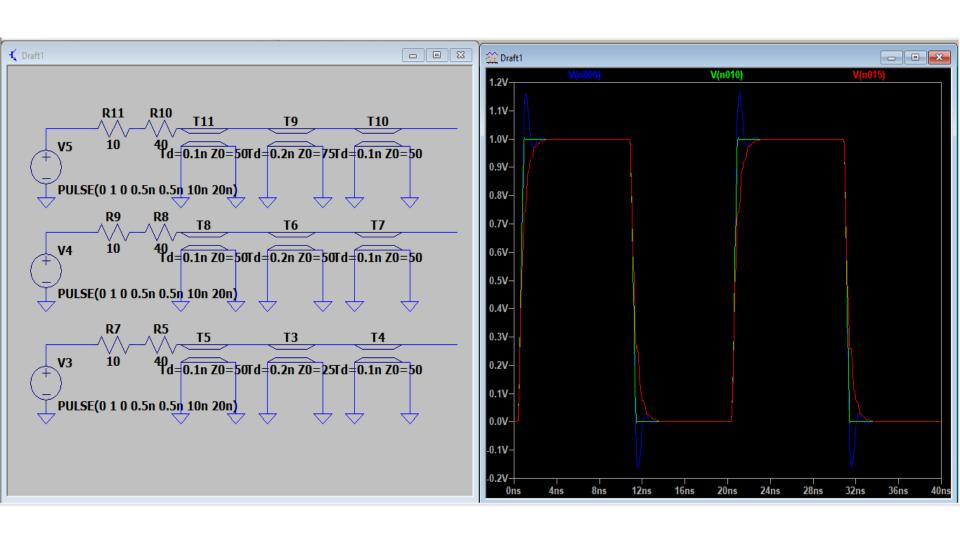

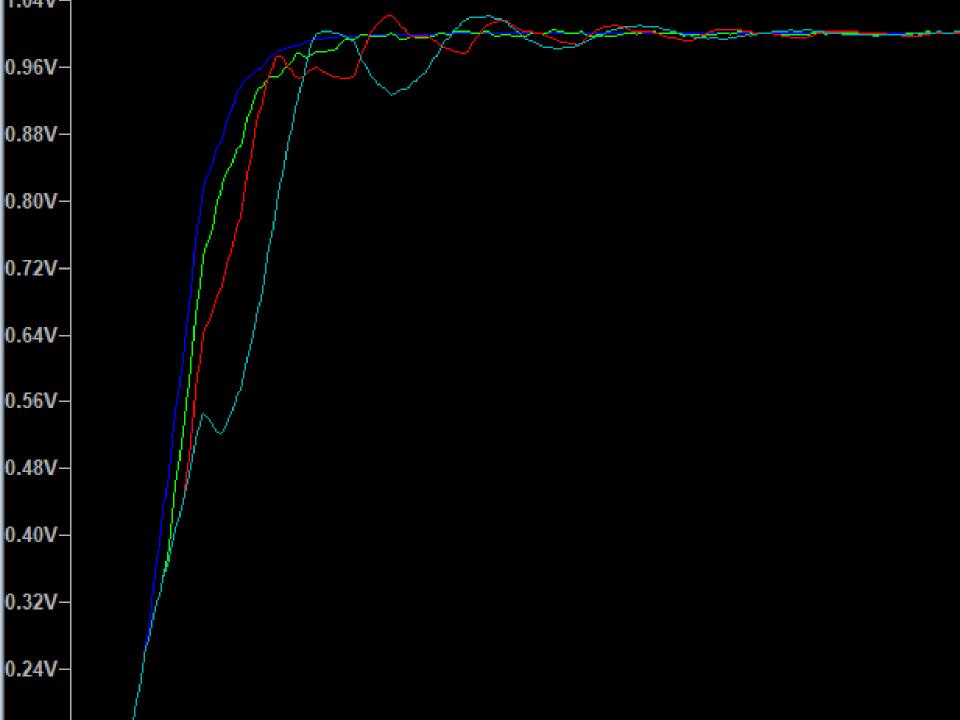

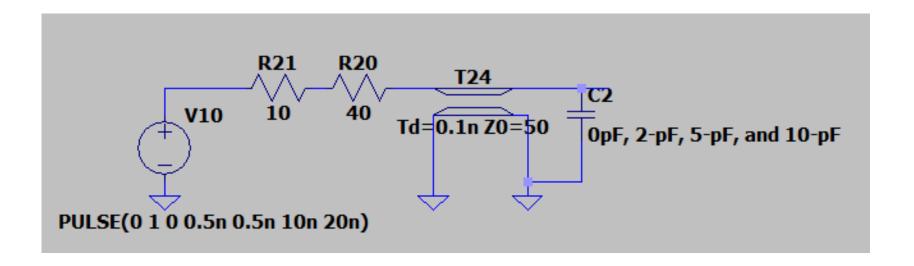

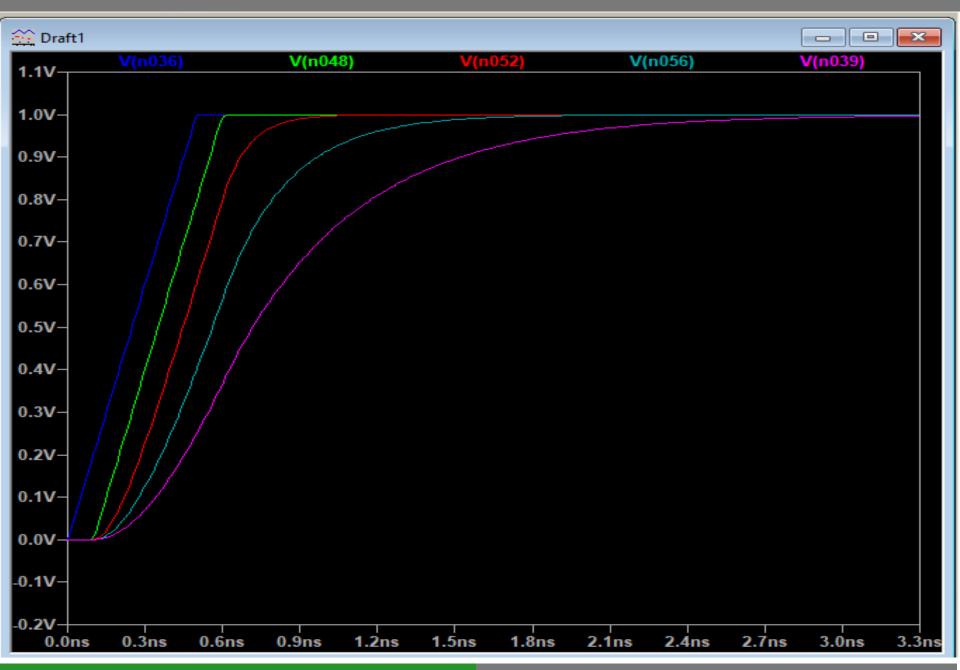

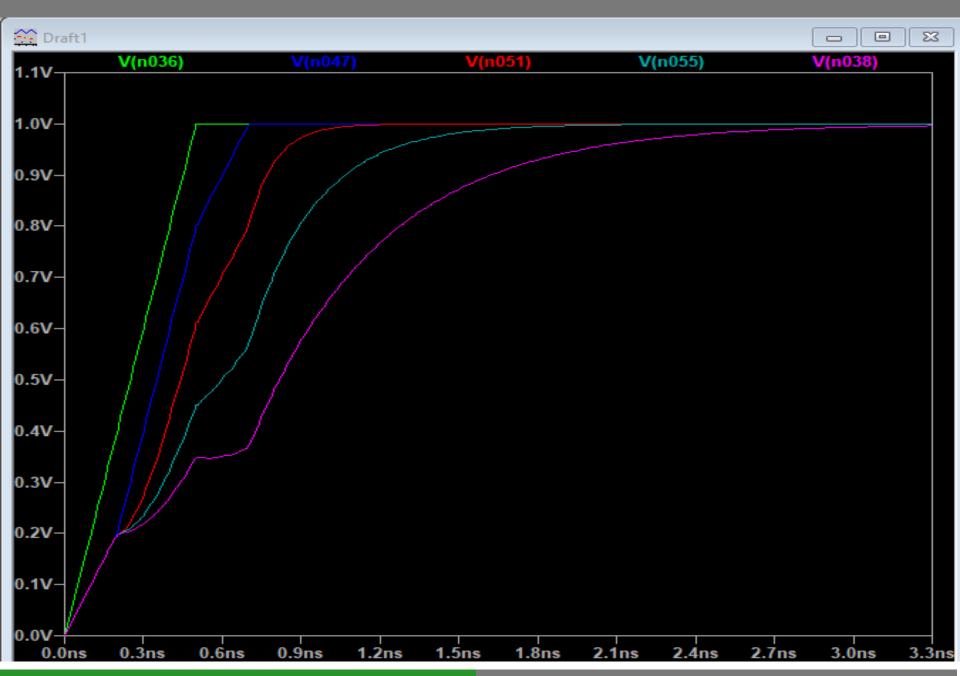

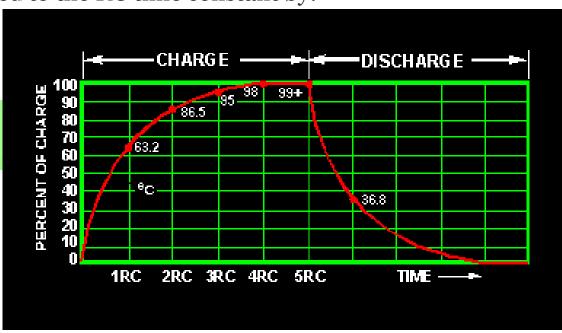

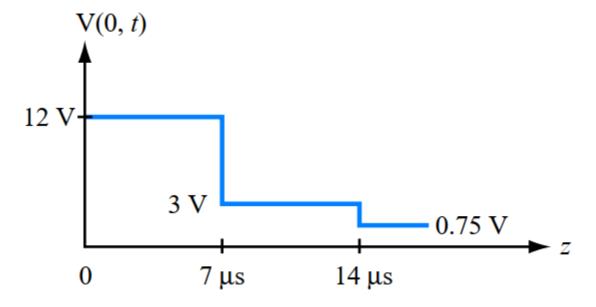

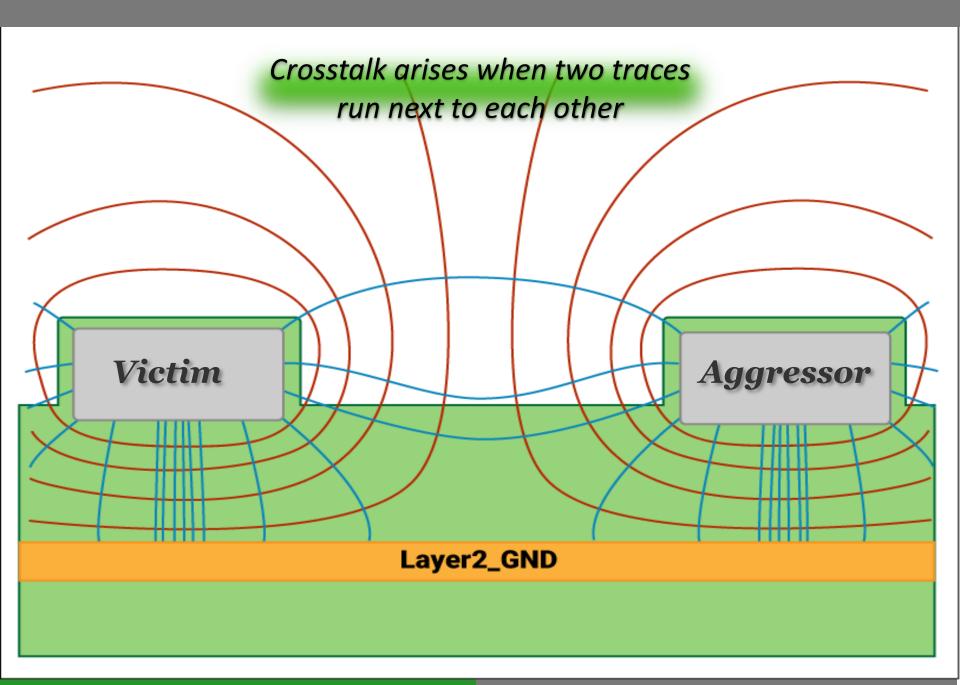

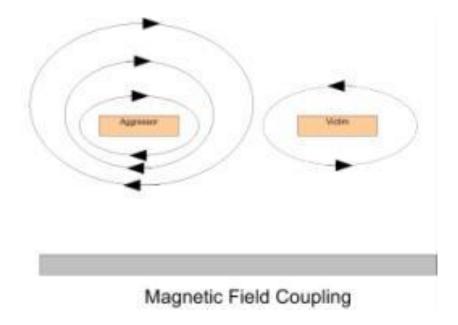

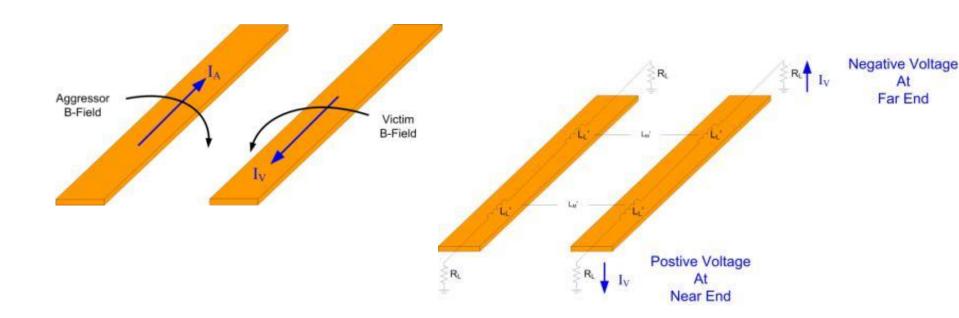

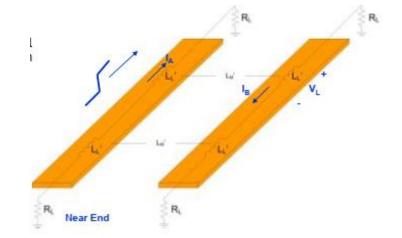

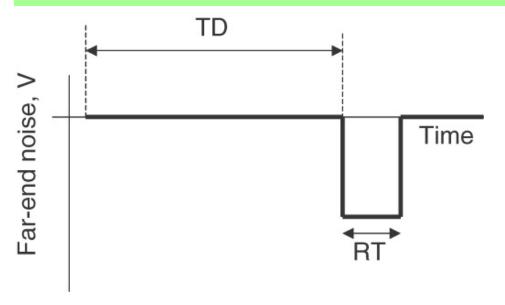

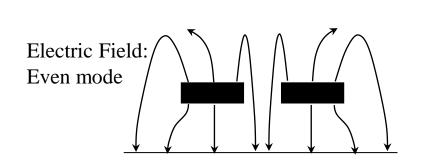

## The speed of an electron in a copper wire?